# Sun<sup>TM</sup> SPOT Theory of Operation *Red Release 5.0*

Sun Labs June 2009

Sun Microsystems, Inc. 4150 Network Circle Santa Clara, CA 95045 U.S.A. 650 960-1300 Part No. 820-1248-10 Document Revision 1.5.0 June 2009 Copyright © 2006-2009 Sun Microsystems, Inc., 4150 Network Circle, Santa Clara, California 95054, U.S.A. All rights reserved.

Sun Microsystems, Inc. has intellectual property rights relating to technology described in this document. In particular, and without limitation, these intellectual property rights may include one or more patents or pending patent applications in the U.S. or other countries.

This product or document is protected by copyright and distributed under licenses restricting its use, copying, distribution, and decompilation. No part of this product or document may be reproduced in any form by any means without prior written authorization of Sun and its licensors, if any. Third-party software, including font technology, is copyrighted and licensed from Sun suppliers.

Parts of the product may be derived from Berkeley BSD systems, licensed from the University of California. UNIX is a registered trademark in the United States and other countries, exclusively licensed through X/Open Company, Ltd.

Sun, Sun Microsystems, the Sun logo, Java, J2EE, J2SE, JDK, JVM, Solaris, and Sun Fire are trademarks or registered trademarks of Sun Microsystems, Inc. in the United States and other countries. All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the US and other countries. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc.

ORACLE is a registered trademark of Oracle Corporation.

The OPEN LOOK and Sun™ Graphical User Interface was developed by Sun Microsystems, Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Xerox to the Xerox Graphical User Interface, which license also covers Sun's licensees who implement OPEN LOOK GUIs and otherwise comply with Sun's written license agreements.

U.S. Government Rights—Commercial use. Government users are subject to the Sun Microsystems, Inc. standard license agreement and applicable provisions of the Far and its supplements.

DOCUMENTATION IS PROVIDED "AS IS" AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID.

Copyright © 2006-2009 Sun Microsystems, Inc., 4150 Network Circle, Santa Clara, California 95054, Etats-Unis. Tous droits réservés.

Ce produit ou document est protégé par un copyright et distribué avec des licences qui en restreignent l'utilisation, la copie, la distribution, et la décompilation. Aucune partie de ce produit ou document ne peut être reproduite sous aucune forme, par quelque moyen que ce soit, sans l'autorisation préalable et écrite de Sun et de ses bailleurs de licence, s'il y en a. Le logiciel détenu par des tiers, et qui comprend la technologie relative aux polices de caractéres, est protégé par un copyright et licencié par des fournisseurs de Sun.

Des parties de ce produit pourront être dérivées des systémes Berkeley BSD licenciés par l'Université de Californie. UNIX est une marque enregistree aux Etats-Unis et dans d'autres pays et licenciée exclusivement par X/Open Company Ltd.

Sun, Sun Microsystems, le logo Sun, Java, J2EE, J2SE, JDK, JVM, Solaris, et Sun Fire sont des marques de fabrique ou des marques déposées, ou marques de service, de Sun Microsystems, Inc. aux Etats-Unis et dans d'autres pays. Toutes les marques SPARC sont utilisées sous licence et sont des marques de fabrique ou des marques déposées de SPARC International, Inc. aux Etats-Unis et dans d'autres pays. Les produits portant les marques SPARC sont basés sur une architecture développée par Sun Microsystems, Inc.

ORACLE est une marque déposée registre de Oracle Corporation.

L'interface d'utilisation graphique OPEN LOOK et Sun™ a été développée par Sun Microsystems, Inc. pour ses utilisateurs et licenciés. Sun reconnaît les efforts de pionniers de Xerox pour la recherche et le développement du concept des interfaces d'utilisation visuelle ou graphique pour l'industrie de l'informatique. Sun détient une licence non exclusive de Xerox sur l'interface d'utilisation graphique Xerox, cette licence couvrant également les licenciés de Sun qui mettent en place l'interface d'utilisation graphique OPEN LOOK et qui en outre se conforment aux licences écrites de Sun.

CETTE PUBLICATION EST FOURNIE "EN L'ETAT" ET AUCUNE GARANTIE, EXPRESSE OU IMPLICITE, N'EST ACCORDEE, Y COMPRIS DES GARANTIES CONCERNANT LA VALEUR MARCHANDE, L'APTITUDE DE LA PUBLICATION A REPONDRE A UNE UTILISATION PARTICULIERE, OU LE FAIT QU'ELLE NE SOIT PAS CONTREFAISANTE DE PRODUIT DE TIERS. CE DENI DE GARANTIE NE S'APPLIQUERAIT PAS, DANS LA MESURE OU IL SERAIT TENU JURIDIQUEMENT NUL ET NON AVENU.

## **Contents**

| Sun™ Small Programmable Object Technology (Sun SPOT) Theory of Operation | 5  |

|--------------------------------------------------------------------------|----|

| Sun SPOT Development Kit                                                 | 5  |

| eSPOT Main Board.                                                        | 7  |

| Main Processor.                                                          | 7  |

| Main Board Communication.                                                | 9  |

| <u>USB</u>                                                               | 9  |

| SPI                                                                      | 9  |

| Programmable Input/Output (PIO)                                          | 10 |

| Memory                                                                   | 10 |

| Power Circuit                                                            | 11 |

| Deep Sleep, Idle, and Run Modes                                          | 12 |

| Battery                                                                  | 13 |

| Battery Warnings                                                         | 13 |

| Power Controller                                                         | 14 |

| Wireless Radio.                                                          | 15 |

| Antenna                                                                  | 17 |

| eSPOT Daughterboards.                                                    | 18 |

|                                                                          |    |

| eDemo Board Hardware                                                     |    |

| Configuration Memory.                                                    |    |

| LEDs.                                                                    |    |

| Push Buttons.                                                            |    |

| GPIO                                                                     |    |

| High Current Driver.                                                     |    |

| Analog to Digital Conversion.                                            |    |

| Temperature Sensor.                                                      |    |

| Accelerometer                                                            |    |

| Accelerometer Self Test                                                  |    |

| Light Sensor.                                                            |    |

| Electrical Characteristics.                                              |    |

| Absolute Maximum Ratings.                                                |    |

| DC Characteristics - eSPOT J2 Connector                                  |    |

| DC Characteristics - eDEMO I/O Connector P1                              | 26 |

| eDemo Software                               | 27 |

|----------------------------------------------|----|

| Overall Operation.                           | 27 |

| Functions                                    | 27 |

| Pulse Width Modulation                       | 27 |

| LEDs.                                        | 28 |

| Pulse Width Generation.                      | 28 |

| Pulse Width Detection.                       | 28 |

| Tone Generation                              | 28 |

| Servo Controller                             | 28 |

| Analog/Digital Conversion                    | 29 |

| Interrupt Detection                          | 29 |

| EEPROM Access                                | 29 |

| I/O Pin Manipulation.                        | 30 |

| Register Control                             | 30 |

| Memory                                       | 30 |

| Miscellaneous Functions                      | 30 |

| Federal Communications Commission Compliance | 31 |

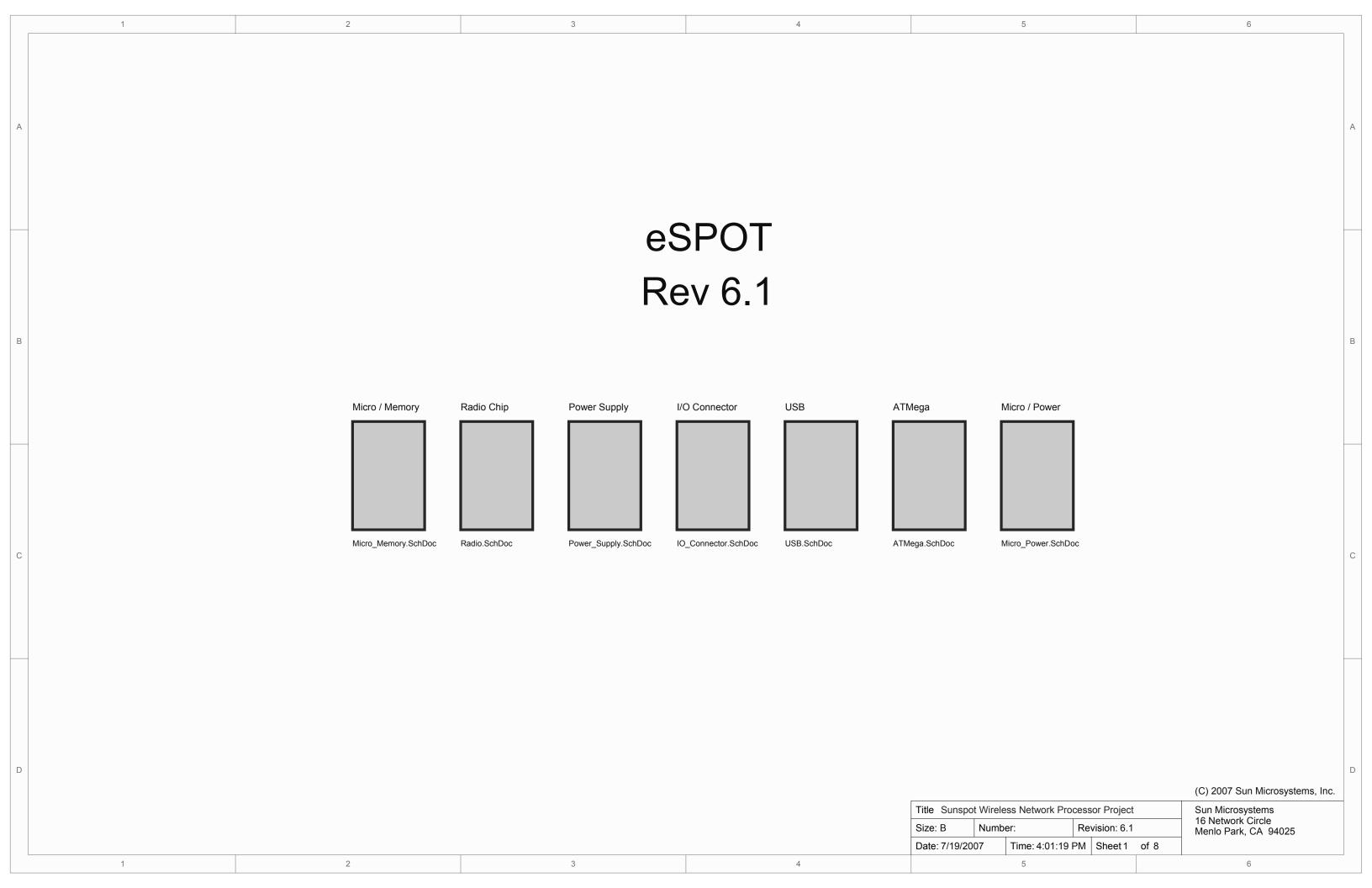

| eSPOT & eDemo Board Schematics and Assembly  | 33 |

|                                              |    |

# Sun<sup>TM</sup> Small Programmable Object Technology (Sun SPOT) Theory of Operation

This document describes the Sun Small Programmable Object Technology (SPOT) hardware platform. It describes

- The development kit contents

- The main board, the eSPOT hardware

- Requirements for any eSPOT daughterboards

- The supplied daughterboard, the eDemo board

## Sun SPOT Development Kit

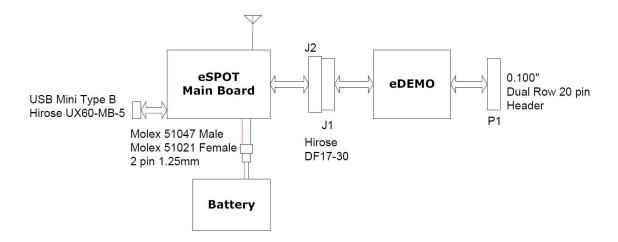

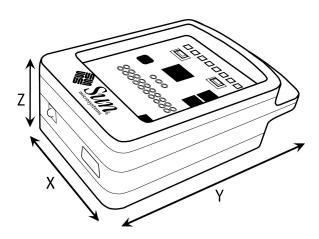

The current configuration of the Sun SPOT platform, the eSPOT, has a main processor running the Java VM "Squawk" and which serves as an IEEE 802.15.4 wireless network node. The eSPOT has flexible power management and can draw from the rechargeable battery or the USB host, or be externally powered.

The Sun SPOT is designed to be a flexible development platform, capable of hosting widely differing application modules. The Sun SPOT development kit, as supplied, contains two different configurations. One of the configurations includes a demonstration application module, the eDemo board.

The configurations supplied in the kit are:

- **Basestation** The basestation has an eSPOT main board without a battery or an application board. Power is supplied by a USB connection to a host workstation. The basestation serves as a radio gateway between other Sun SPOTs (and theoretically other 802.15.4 devices) and the host workstation

- **eSPOT** This unit contains the main board with a rechargeable LI-ION prismatic battery and an example of an eSPOT daughterboard, the eDEMO board.

The development kit also contains

- A wall-mount bracket for the eSPOT.

- An eSPOT module adapter. This plastic replaces the top eSPOT plastic and allows the eSPOT to be attached to a larger circuit board.

Other plastics may be available from the Sun SPOT team in the near future.

The eDEMO board is an example of the class of daughterboards that are compatible with the eSPOT main board. The eDemo board contains a 3-axis accelerometer, an ambient light sensor, a temperature sensor, eight tricolor LEDs, two push buttons, six analog input pads, four high-current high-voltage output pads, and five general I/O pads.

## eSPOT Main Board

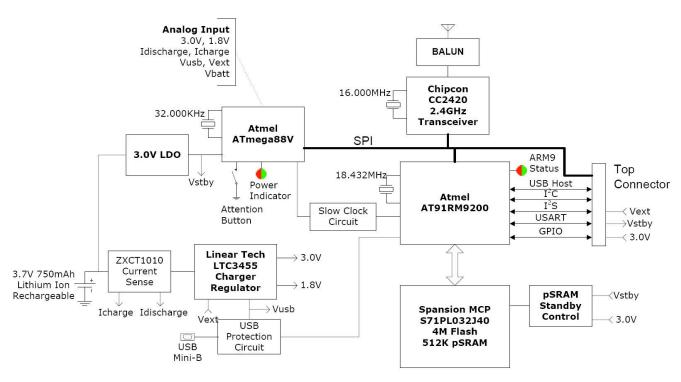

The eSPOT main board contains the

- Main processor

- Memory

- Power management circuit

- 802.15.4 radio transceiver and antenna

- Battery connector

- Daughterboard connector

## Main Processor

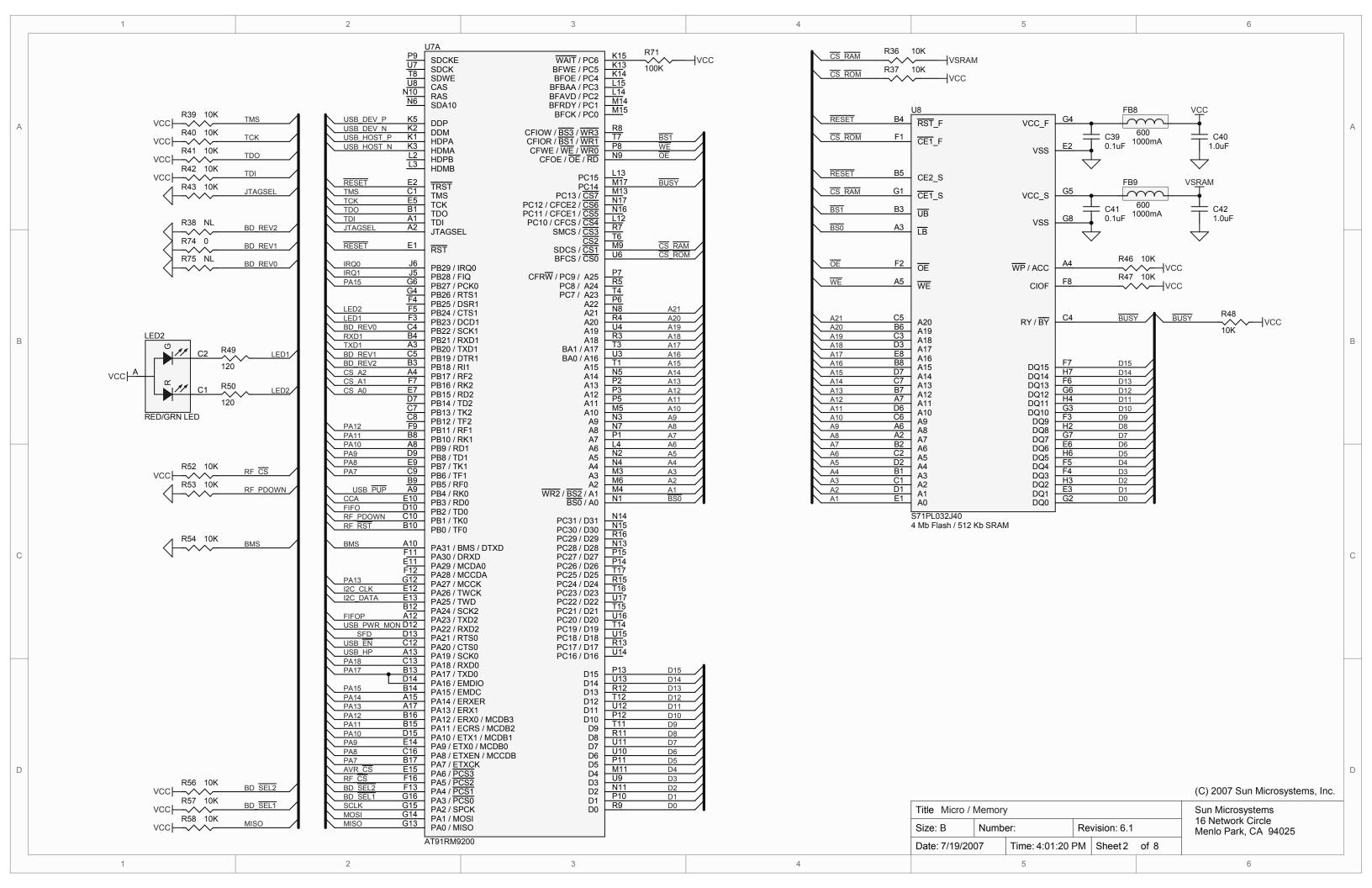

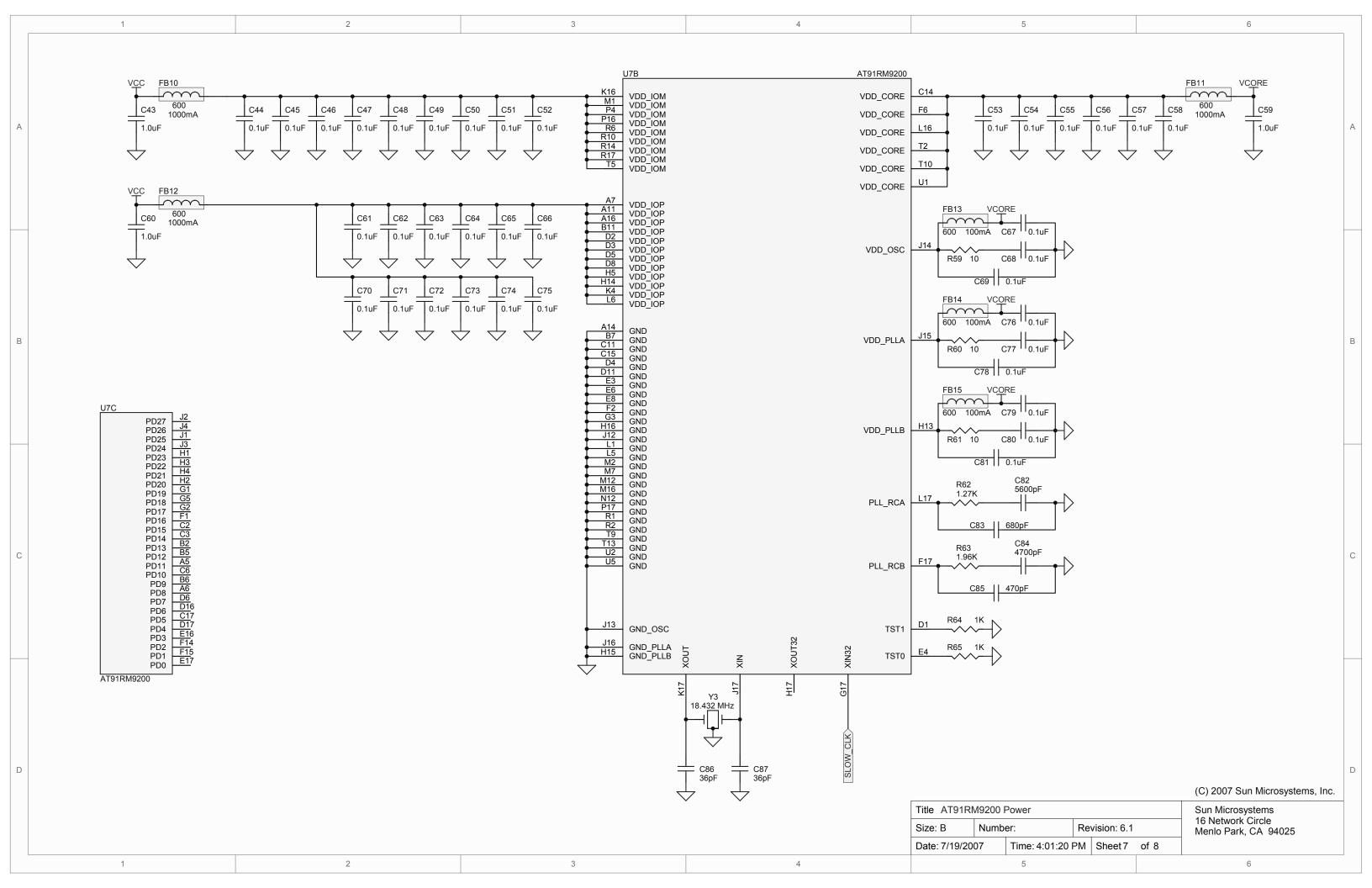

The main processor is an Atmel AT91RM9200 system on a chip (SOC) integrated circuit. This unit incorporates the ARM920T ARM Thumb processor, based on the v4T ARM architecture ARM9TDMI. The unit is packaged in a 256-pin ball grid array package measuring 15mm square and does not require a heat sink. Power to the SOC is 3.0V I/O voltage and 1.8V core voltage. In normal operation, it consumes approximately 44mW core power. The ARM executes at 180MHz maximum internal clock speed based on a software controllable phase lock loop/oscillator. The SOC contains a 64-way associative 16Kbyte data cache and a 16Kbyte instruction cache. The ARM9 uses a standard ARMv4 memory management unit with 64-entry instruction translation lookaside buffer (TLB) and 64-entry data TLB. The unit has standard IEEE 1149.1 JTAG boundary scan on all digital pins. These signals are brought to test pads on the bottom of the eSPOT board. This requires a production test fixture with pogo pin connector to access these pads. The JTAG signals are pulled up by 10K resistors to V<sub>CC</sub>.

The external memory is controlled and accessed using the external bus interface (EBI) module. The EBI contains a static memory controller, SDRAM controller, and burst flash controller. The eSPOT uses the static memory controller for interfacing to Flash and pSRAM memories. The SDRAM and burst flash controllers are not used and powered down. The static memory controller is configured to boot from Flash memory. The external memory data bus is a 16-bit data path with byte-wide and word-wide access. It uses twenty-one address bits A1-A21 for word address with BS1 (UB) and BS0 (LB) byte and word address. CS\_RAM (CS1) enables pSRAM access and CS\_ROM (CS0) accesses FLASH memory. Memory is read when chip select and OE are asserted and written when chip select and WE are asserted.

The ARM9 is reset by the power controller as part of the power up and power down sequence. Reset also disables the pSRAM during power change to prevent accidental writes to memory.

The ARM920T has two clock sources that can be selected: BCLK and FCLK. The selected clock source is used to generate its global clock, GCLK. FCLK is controlled from a software programmable phase lock loop (PLL). BCLK is controlled from the 32.768KHz real time clock oscillator and is enabled on startup. Initialization software then configures the phase lock loop and switches from BCLK to the faster FCLK.

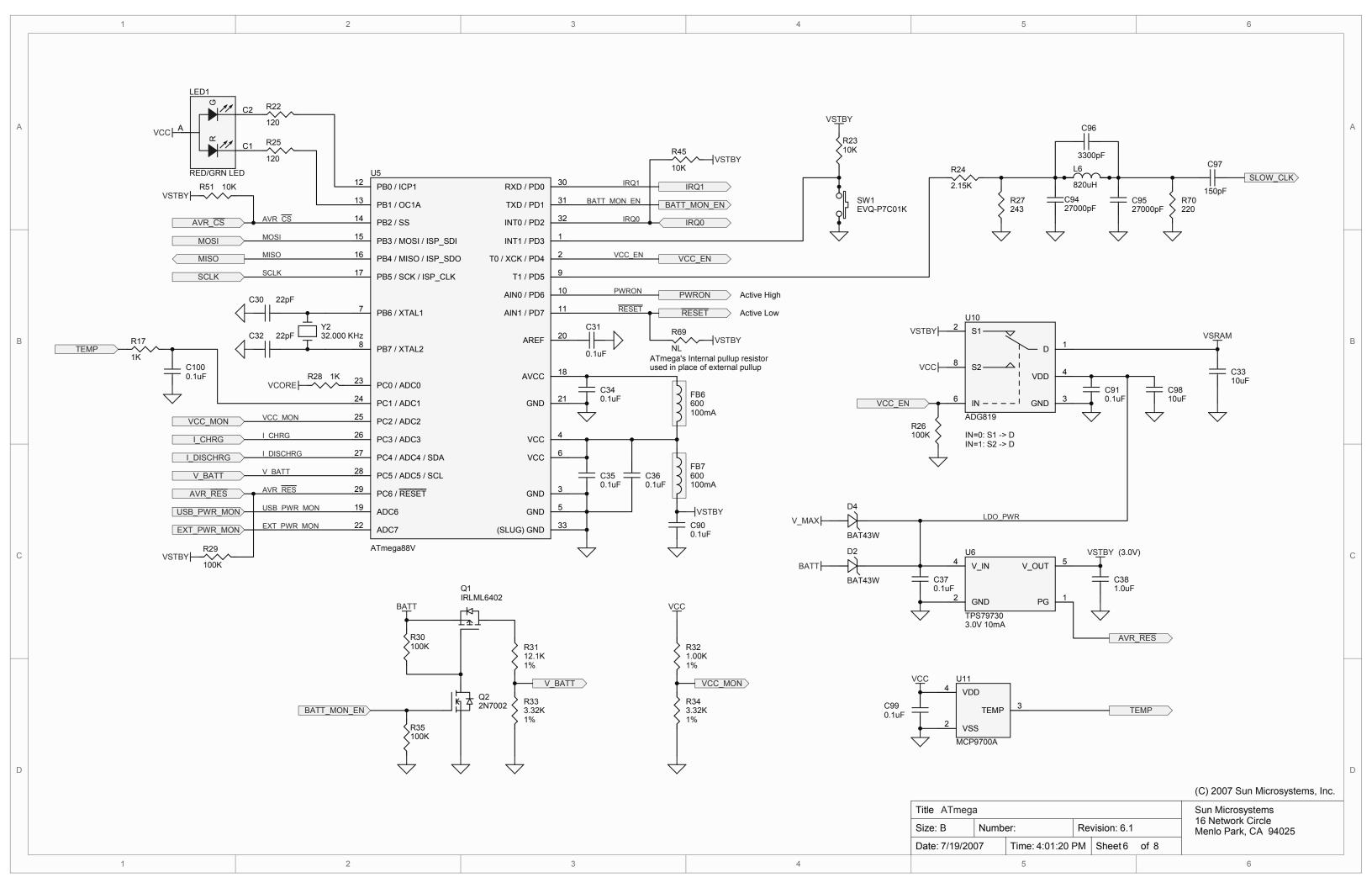

Rather than use a slow crystal with a 900msec start up time, we generate an instant 32.7 KHz square wave from the power controller. We run the square wave through an attenuator and a three-pole Cauerelliptic low-pass filter to create a 120 mV 32.7 KHz sine wave to the real time clock oscillator. This clock starts when  $V_{\text{ddio}}$  reaches 1.5 V and shuts off when the ARM is placed into deep-sleep.

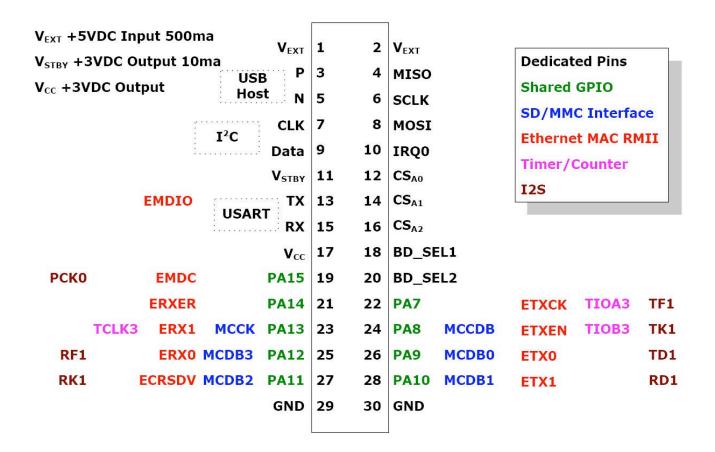

The SOC has a large collection of peripheral interface units. These include USB host port, USB device port, Ethernet MAC, programmable I/O (PIO) controller, serial peripheral interface (SPI) controller, TWI two-wire (I2C) interface, universal synchronous/asynchronous serial interface (USART), serial synchronous controller (I2S), multimedia card interface, three 16-bit counter/timers and system timers. The unit also contains a real-time clock which is unused. The SOC also contains a peripheral DMA controller (PDC) for fast direct access to USART, I2S, SPI, and memory channel.

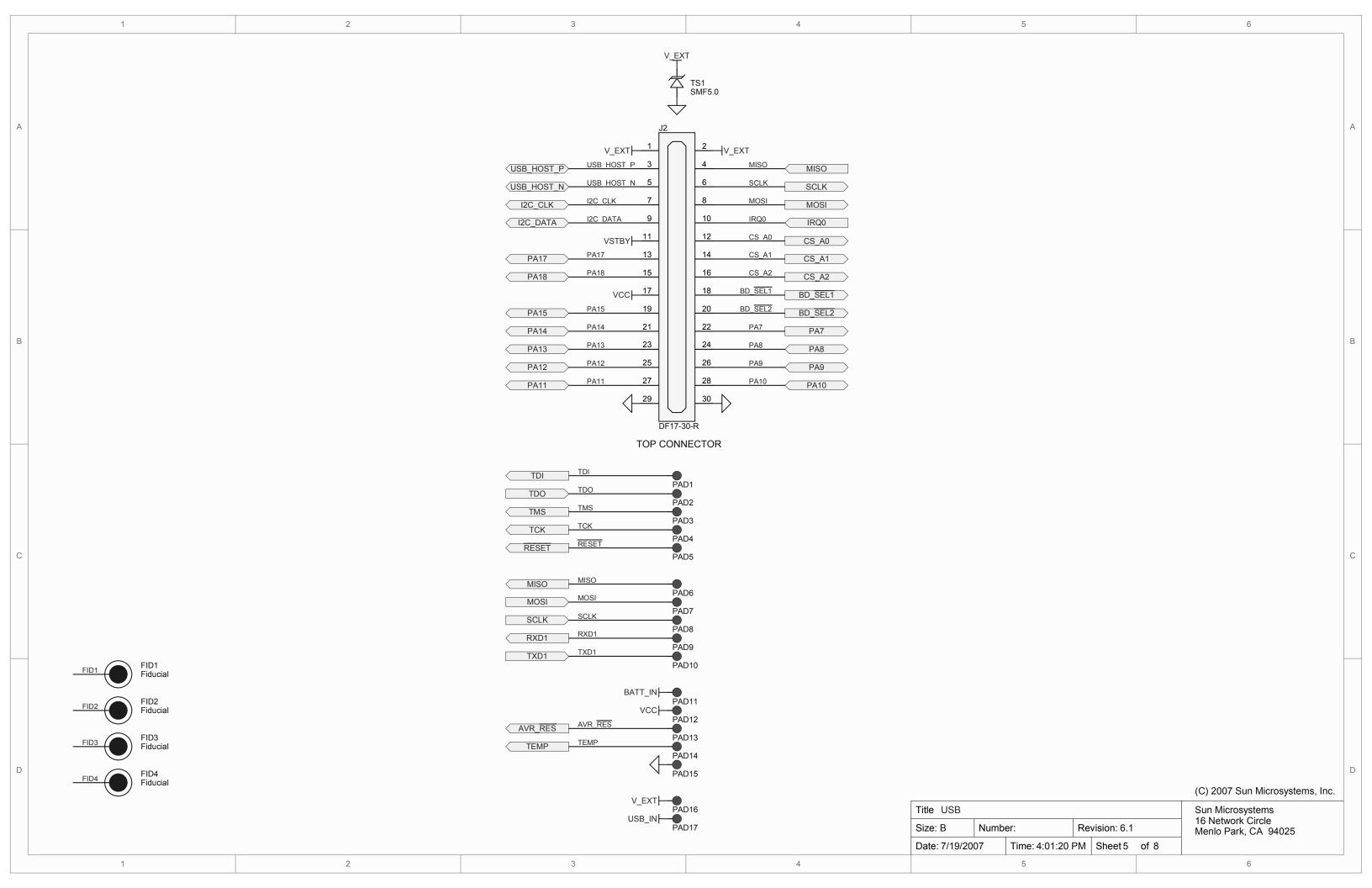

The USB host port, one USART, and the multimedia card, TWI, I2S and Ethernet MAC interfaces are not used directly in the current eSPOT implementation although all signals are brought to the interboard connector. These peripherals could be used provided the appropriate physical interface and driver software. As this is a small unit, not all devices can be utilized simultaneously. The pin out description of the inter-board connector is illustrated below.

#### Main Board Communication

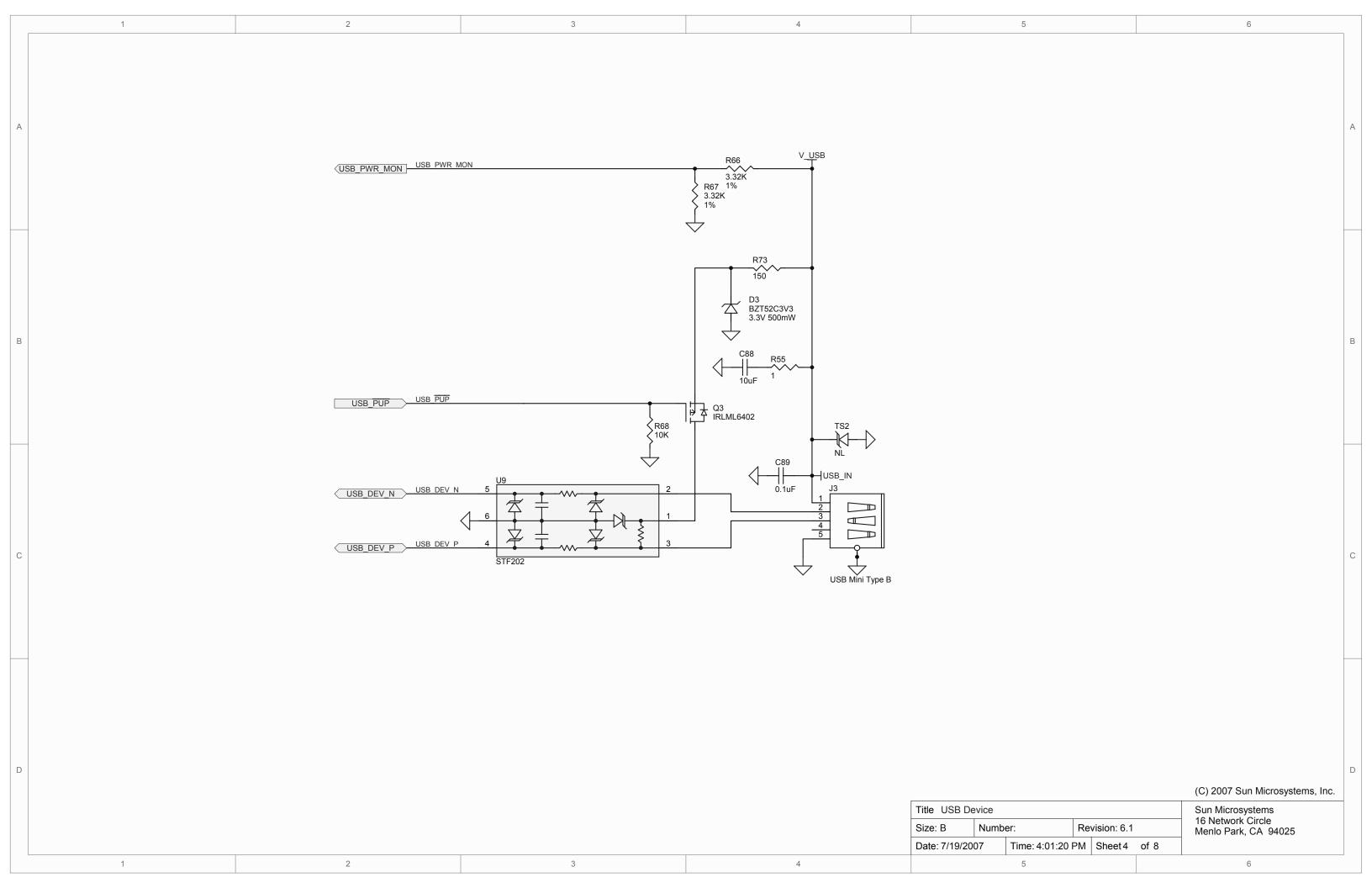

#### USB

The USB client has termination and ESD protection circuit U9 to a type B mini USB connector. The USB device is USB 1.1 and USB 2.0 compliant. A 1.5K resistor pulled to 3.3V from V<sub>usb</sub> is switched on by FET Q3 when USB\_PUP is asserted. The 1.5K resistor is on the D+ signal indicating full speed device during start-up. The USB client supports CDC Abstract Control Mode (ACM) modem interface for serial communication. Currently no other endpoints are supported. Basestation SPOTs interact with the host workstation principally through the USB client.

#### **SPI**

The SPI interface is the primary interface to most on-board devices and for inter-board communications. Within the eSPOT main board, SPI is the communication channel to the radio transceiver IC CC2420 and the power controller.

SPI communication relies on four signals:

- MOSI (Master Out, Slave In)

- MISO (Master In, Slave Out)

- SCLK (Synchronous Clock)

- CS (Control Strobe)

The ARM9 is master in all conditions. PIO signals provide the active low control strobes (CS). MISO and MOSI are the tri-stateable serial data lines and the SCLK is the synchronized clock for the data originating from the master.

SPI shifts out bytes most significant bit first, synchronized either to the rising or falling edge of SCLK. While it is shifting out on MOSI, it is shifting in to a holding register from MISO. Chip select is asserted prior to shifting and deselected after a byte transfer. Each slave device has a unique chip select and removes tristate from MISO only when the slave is selected.

The CS for the power controller is AVR\_CS (PA6/PCS3). The CS for the CC2420 radio transceiver is RF\_CS (PA5/PCS2). Inter-board chip select uses a primary "board" select of BD\_SEL1 (PA3/PCS0) and BD\_SEL2 (PA4/PCS1). A secondary three bit address allows selection of eight devices for each board select. The secondary address, from least significant bit to most is CS\_A0 (PB15), CS\_A1 (PB16) and CS\_A2 (PB17). The secondary address lines must be selected and stable prior to BD\_SELx asserted and must remain stable until after BD\_SELx is deasserted. For stacking boards, BD\_SEL1 selects the board nearest the main board, and BD\_SEL2 selects the stacking board. BD\_SEL1 is used when only one application board is present.

Every application board is required to have a small SPI EEPROM selectable when  $CS_A0 = '1'$ ,  $CS_A1 = '1'$  and  $CS_A2 = '1'$ . This memory is for board identification and configuration information.

#### Programmable Input/Output (PIO)

The bicolor LED closest to the center of the unit is controlled by the PIO interface. The red LED2 uses PIO PB24 and green LED1 uses PIO PB23. USB power control signals USB\_PUP output from PIO PA21 controls USB pull-up enable, USB\_PWR\_MON is high when USB power available and input to PIO PA22, USB\_EN is output from PIO PA20 and controls the suspend line on the power regulator, USB\_HP is output from PIO PA19 which sets power control into high power mode when high.

PIO bits also control signals or read status to and from the radio transceiver. The signals are:

- FIFOP input to PIO PA23 indicates RX fifo full

- FIFO input to PIO PB2 indicates bytes are in the receive buffer

- RF PDOWN (VREG EN) output from PIO PB1 turns the local regulator on

- SFD input to PIO PB4 indicates start of frame

- CCA input to PIO PB3 indicates clear channel assessment

- RF RST output from PIO PB0 forces the transceiver to reset when asserted low

For more information, refer to the ARM920T technical specification and the AT91RM9200 datasheet from the Atmel website.

## Memory

Memory is a single Spansion S71PL032J40, a multichip package (MCP) consisting of a 4MByte NOR Flash memory and a 512KByte pseudo-static random access memory (pSRAM). The Flash memory and pSRAM die are stacked on a single 56-pin fine pitch ball grid array, 9mm x 7mm. The access time

of the pSRAM is 70nsec and the flash memory is 65nsec. The pSRAM is self-refreshing and automatically enters power down when not selected for access. Memory contents are maintained as long as a power supply USB, external or battery is connected, even during periods of off or "deep-sleep."

Flash and pSRAM are both 16-bit data paths and are byte and word accessible. There are 21 address lines, upper and lower byte strobes, output enable, write enable, pSRAM chip selects and flash chip select. The BUSY signal from the MCP can indicate refresh in progress, write to flash in progress to hold off the processor. BUSY goes to PIO PC14 on the processor. The write protect (WP) is disabled by a pullup to  $V_{\rm CC}$ .

The unit is powered from a single 3.0V supply with individual and separate power pins for Flash and pSRAM. Power to the pSRAM is controlled by a FET switch U10, Analog Devices ADG819. This switch is controlled by the power controller. When the unit is in deep sleep, it switches to a very low current standby voltage which maintains the memory contents. When the power controller powers the processor, the switch is set to use the higher current  $V_{CC}$  source. Power consumption of the pSRAM during deep-sleep is approximately  $8\mu A$ . Power is removed from flash during deep-sleep. During normal operation, pSRAM consumes 25ma and Flash consumes 22ma.

Flash memory uses a common flash interface with erase, sector write and random and page mode read operations. The Flash memory is divided into 4Kword (boot, both top and bottom) and 32Kword sectors with one million write sector cycles.

Flash is preprogrammed with the bootloader, VM, base class libraries and applications at the factory. The customer lockable area (0x000040-0x00007f) is programmed at the factory with a 64-bit IEEE extended unique identifier (EUI). The IEEE EUI is read only and is a concatenation of a 24-bit company code (OUI) and with a 40-bit extension that is unique for each SPOT.

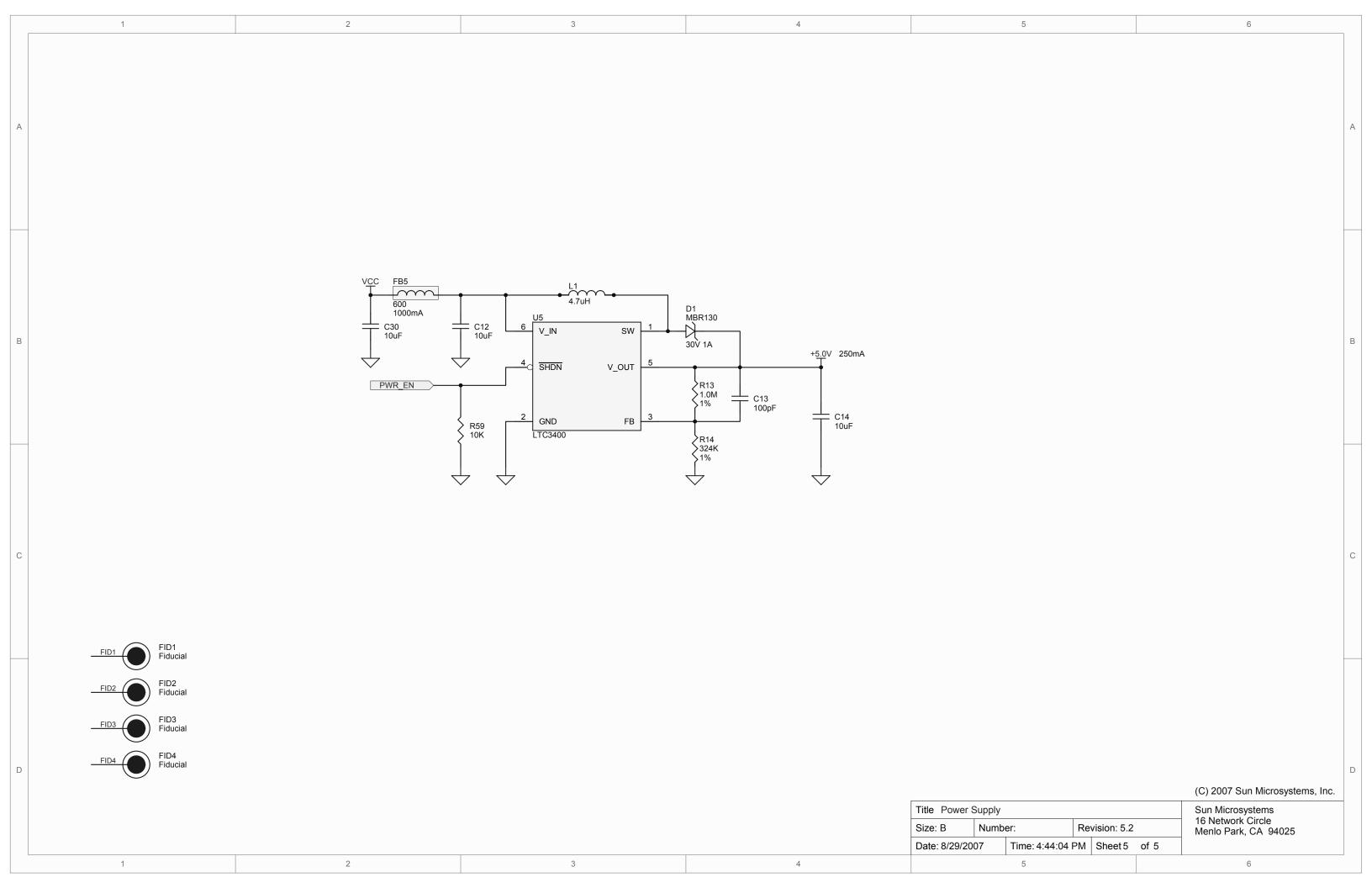

## **Power Circuit**

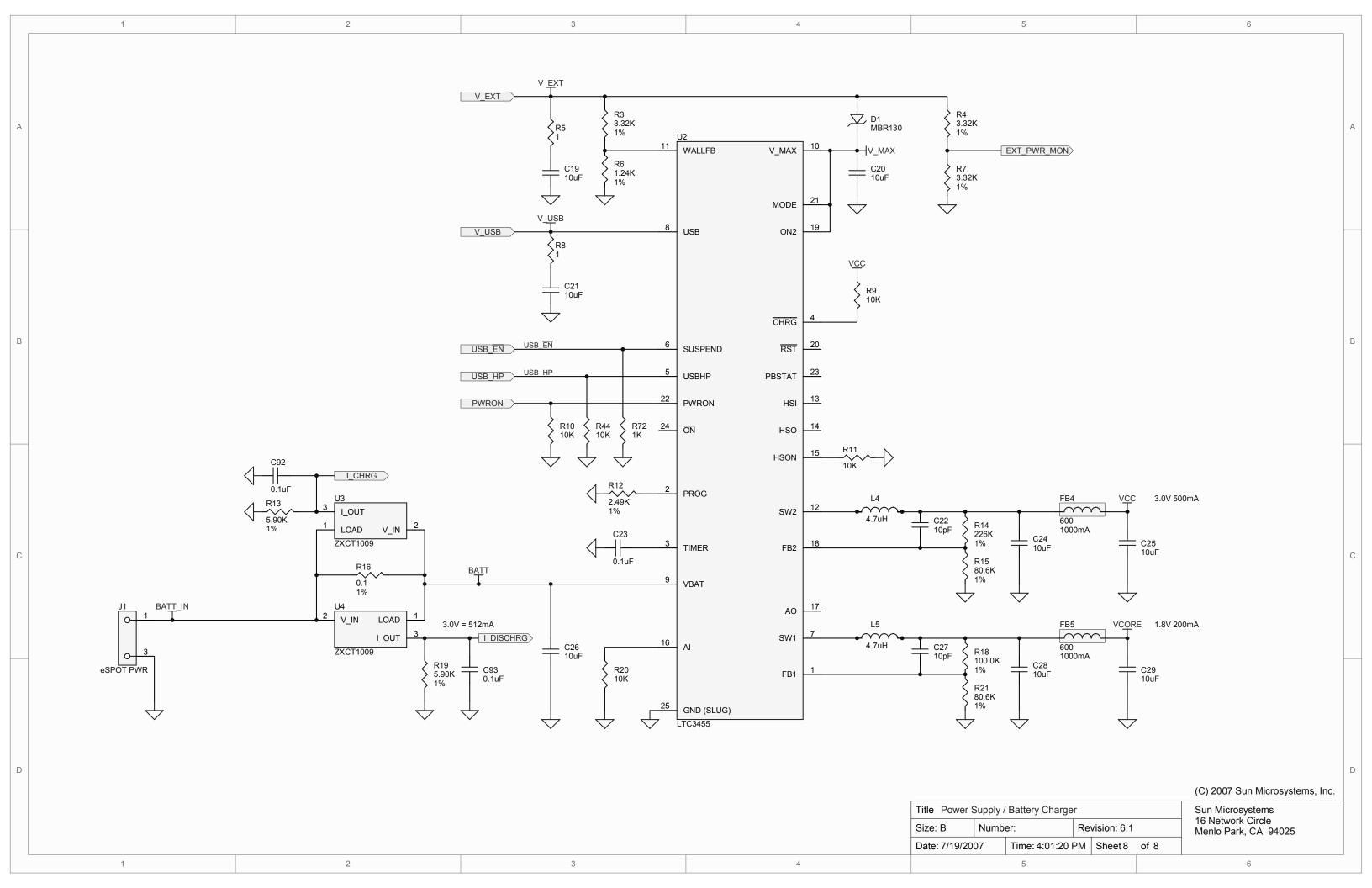

The eSPOT can be powered with any combination of rechargeable battery, external voltage or the USB Host. The power circuit charges the battery, regulates the power to the main and application boards, provides standby power during deep-sleep, maintains a 64-bit millisecond clock with alarm, monitors power levels and manages the attention button and power LEDs.

The power regulation portion of the circuit is the Linear Technology LTC3455 U2. The LTC3455 is an integrated Li-ION battery charger, USB power manager and dual switching regulator. The current mode step-down switchers run at 1.5MHz and output 3.0V at 500ma ( $V_{\rm CC}$ ) and 1.8V at 200ma ( $V_{\rm core}$ ). The  $V_{\rm CC}$  switcher is similar to the LTC3406 and the  $V_{\rm core}$  switcher is similar to the LTC3405. The Li-ION battery charger is constant current charger similar to the LTC4053. The switching regulators (not the charger) are turned on by the PWRON signal from the power microcontroller. The LTC3455 is packaged in a 24-pin QFN (Quad Flat package no leads) 4mm square.

The LTC3455 current limits the USB current to 100ma when USB\_HP is low and 500ma when USB\_HP signal is high. USB\_HP is controlled by the ARM9 PIO PA19. External voltage is not affected by USB\_HP; however, 100ma incoming current only allows the ARM9 to run in order to negotiate for more power. If the SPOT is running without a battery, powered only by the USB, the application board and radio should be powered down until the device is fully enumerated and can set the higher current. The ARM9 can shut down the USB regulator and battery charger with the USB\_EN

signal. USB voltage and external voltage have a "snubbing" RC filter to protect against insertion voltage surges.

When either external or USB power is applied and the battery is below 4.05V, a timed constant current charge starts. This should last approximately three hours and the maximum charge current is 450ma. If the battery below 3.0V, the regulators will not start. If the die reaches 105°C, charge current is greatly reduced.

A very low quiescent current LDO voltage regulator, TI TPS79730 U6, generates 3.0V for standby voltage needs. The LDO power input is from any of the power sources and provides constant uninterruptable power to the Atmega88 microcontroller, the pSRAM portion of the MCP memory and the pullup on the attention button. The LDO also generates a brown-out detect which pulls the reset low on the Atmega88 should the voltage drop below the Atmega88 operating parameters. If the battery is not present and power is discontinued or if the battery voltage falls below 3.0V, the real time clock or alarm will not function

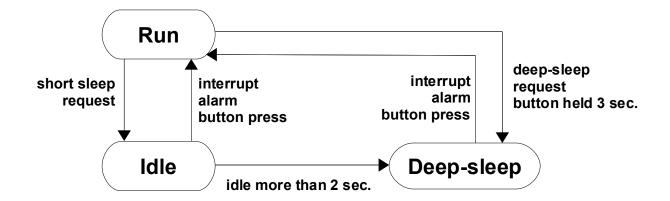

## Deep Sleep, Idle, and Run Modes

Sun SPOTs have power conservation firmware that uses three modes of operation:

**Run** Basic operation with all processors and radio running. Power draw for the eSPOT board in Run mode is between 70ma and 120ma. The application daughter board can consume up to 400ma if enabled.

**Idle** ARM9 clocks are shut off and the radio is off. Idle mode power consumption is about 24ma.

**Deep-sleep** All regulators are shut down except for the standby LDO, the power-control Atmega and pSRAM. Deep-sleep power consumption is  $32\mu A$ . Typical start-up time from deep-sleep is about 2msec to 10msec.

Deep-sleep can not be entered if the radio is on, if external power is supplied, or if USB power is on.

Deep-sleep and idle are entered programmatically. Deep-sleep can also be entered by holding the attention button more than 3 seconds. Waking the processor up from deep-sleep can be done with the alarm, an external interrupt or pressing the attention button. Power consumption mode transitions are illustrated below.

The sequence of events for start up when it is initiated is first the external interrupt is disabled, the ARM9 is held in reset, the internal power monitor ADC begins and then PWRON to the power regulator is asserted. The ADC tracks the  $V_{CC}$  and  $V_{core}$  voltages as the regulators reach full voltage. When  $V_{CC}$  reaches 1.1V, the internal timer used to generate the 32.7KHz start up clock to the ARM9 starts oscillating. When  $V_{CC}$  has reached a stable 3.0V, the pSRAM voltage is switched from standby LDO to  $V_{CC}$  and the ARM9 is brought out of reset. Status bits are available to the ARM9 to indicate how the startup was initiated to determine continuing from a known context or restarting.

## **Battery**

The internal battery is a 3.7V 720maH rechargeable lithium-ion prismatic cell. The battery has internal protection circuit to guard against over discharge, under voltage and overcharge conditions. The battery can be charged from either the USB type mini-B device connector or from an external source with a 5V  $\pm 10\%$  supply. Typical shelf life losses at room temperature are about 2% of the batteries capacity per month and the rate can increase with the rise in temperature.

The battery can **not** be changed for another type of battery. The charging and power management systems are tuned for this specific battery. The risks associated with battery substitution are substantial.

The simplest, safest, and easiest way of extending the operating period of a Sun SPOT beyond the length of one battery charge is to provide USB power. There are a variety of USB power dongles available on the market, including AC and battery-powered models.

## Battery Warnings

Do not short-circuit battery. A short-circuit may cause fire, explosion, and/or severe damage to the battery.

Do not drop, hit or otherwise abuse the battery as this may result in the exposure of the cell contents, which are corrosive.

Do not expose the battery to moisture or rain. Keep battery away from fire or other sources of extreme heat. Do not incinerate.

Exposure of battery to extreme heat may result in an explosion.

No other battery substitutions or different chemistry batteries should be used.

Do not bypass the battery protection circuit.

Dispose of batteries properly. Do NOT throw these batteries in the trash. Recycle your batteries, if possible.

#### Power Controller

The power controller is an 8-bit microcontroller Atmel Atmega88. Its firmware is responsible for keeping a 64-bit millisecond real time clock running, waking up the system when an alarm occurs, waking up the system if an external interrupt is seen from the application module, and waking up and putting the system into deep-sleep from the attention button. The power controller also measures the battery voltage, the battery charge current and discharge current,  $V_{CC}$  voltage,  $V_{core}$  voltage,  $V_{ext}$  external voltage, and USB voltage  $V_{usb}$ . The Atmega88 also controls a bicolor LED (Power LED) and indicates various modes and fault conditions through this LED. The Atmega88 has a low frequency 32.000KHz crystal prescaled by 32 for an increment per millisecond of one of the internal timer/counters.

The Atmega88 interacts with the ARM9 through the SPI channel as a slave device and using AVR\_CS (PCS3) as the enable. The first byte sent is the command and subsequent bytes transfer status and parameters to and from the Atmega88. The power controller can interrupt the ARM9

While in run or idle mode, the built-in 10-bit A/D converter measures all of the seven voltage/current levels every 50ms. It uses a 1.1V internal reference for measuring battery voltage and the 3.0V standby regulator as an external reference for all other measurements.

The battery current is measured by monitoring the voltage drop across a  $0.1\Omega$  resistor using high-side current sensors Zetex ZXCT1009 U4 for discharge and U3 for charge. Current measurement resolution is 0.5ma and can measure a maximum of 512ma to or from the battery. The battery voltage is enabled by a FET switch Q1 and Q2 and divided by series resistance. The microcontroller enables this switch only when reading the battery voltage and disables it all other times to minimize current drain.

ACD equations for calculating value to units are as follows.

| Signal            | Equation                                             |

|-------------------|------------------------------------------------------|

| V <sub>batt</sub> | $ADC = \frac{V_{batt} \cdot 1024}{5.1} \qquad volts$ |

| Vcc               | $ADC = \frac{V_{cc} \cdot 1024}{3.904}  volts$       |

| V <sub>core</sub> | $ADC = \frac{V_{core} \cdot 1024}{3.0}  volts$       |

| Signal           | Equation                                          |

|------------------|---------------------------------------------------|

| V <sub>ext</sub> | $ADC = \frac{V_{ext} \cdot 1024}{6} \qquad volts$ |

| V <sub>usb</sub> | $ADC = \frac{V_{usb} \cdot 1024}{6} \qquad volts$ |

| Icharge          | $ADC = I_{charge} \cdot 2$ milliamps              |

| Idischarge       | $ADC = I_{discharge} \cdot 2$ milliamps           |

After each measurement, the values are compared to acceptable ranges of values. If any of these values go outside, the power light indicates a power fault. If the battery is approaching fully discharged state, it shows a low battery indication. If the unit is charging, it shows a charge indication. Voltage ranges are shown in the table below.

| Voltage                | Target    | Error states                   |

|------------------------|-----------|--------------------------------|

| Vcc                    | 3.0V ±10% | 2.7V or > 3.3V power fault     |

| V <sub>core</sub>      | 1.8V ±10% | < 1.62V or > 1.98V power fault |

| V <sub>usb</sub>       | 5.0V ±10% | < 4.5V or > 5.5V power fault   |

| V <sub>ext</sub>       | 5.0V ±10% | < 4.5V or > 5.5V power fault   |

| I <sub>discharge</sub> | < 500ma   | > 500ma power fault            |

| V <sub>batt</sub>      | > 3.25V   | < 3.25V indicates low battery  |

| V <sub>batt</sub>      | > 3.05V   | < 3.05V indicates dead battery |

| I <sub>charge</sub>    | < 5ma     | > 5ma indicates charging       |

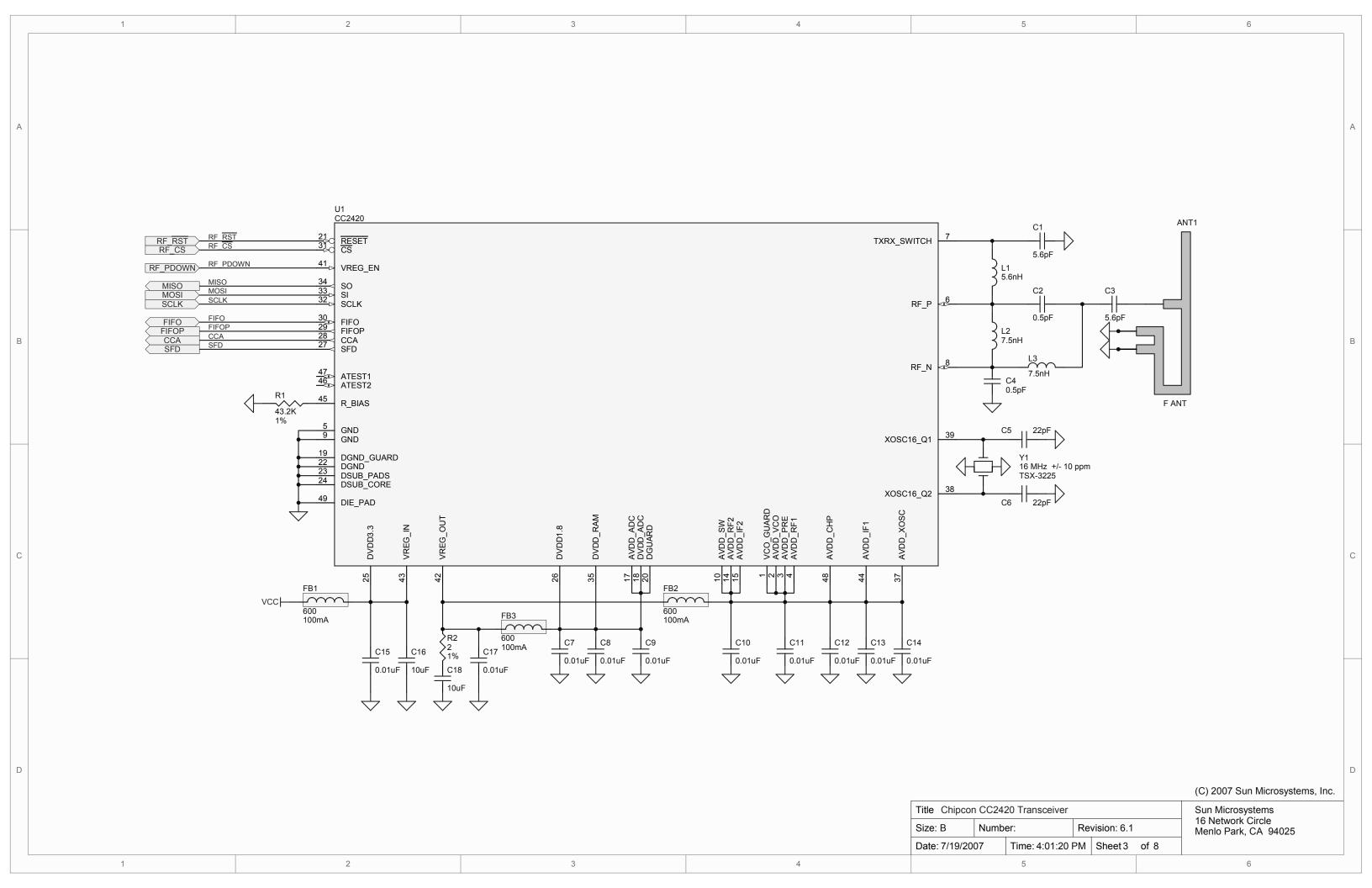

## Wireless Radio

The wireless network communications uses an integrated radio transceiver, the TI CC2420 (formerly ChipCon). The CC2420 is IEEE 802.15.4 compliant and operates in the 2.4GHz to 2.4835GHz ISM unlicensed bands. Regulations for these bands are covered by FCC CFR47 part 15 (USA), ETSI EN 300 328 and EN 300 440 class 2 device (Europe) and ARIB STD-T66 (Japan). Please check with country statutes for appropriate operation.

The IC contains a 2.4GHz RF transmitter/receiver with digital direct sequence spread spectrum (DSSS) baseband modem with MAC support. Other features include separate TX and RX 128 byte FIFOs, AES encryption (currently not supported), received signal strength indication (RSSI) with 100dB sensitivity

and transmit output power setting from -24dBm to 0dBm. Effective bit rate is 250kbps and chip rate is 2000kChips/s. Receive sensitivity is -90dBm.

The digital control and data communications with the CC2420 use PIO port bits and the SPI channel. The CC2420 is a slave SPI bidirectional device addressed when RF\_CS (PCS2) is asserted active low. PIO ports reset the CC2420 (RF\_RST), power it down (RF\_PWDOWN), or check the status of the receive FIFO (FIFO and FIFOP), clear channel assessment (CCA) and start of frame (SFD).

There are 33 configuration and status registers, 15 command registers and two 8-bit registers for the separate transmit and receive FIFOs. The first byte sent to the CC2420 is the address made up of 6-bit address, RAM/Register select (Bit 7) and Read/Write select (Bit 6). Following bytes are data read from or written to the CC2420.

The CC2420 is housed in a 48pin quad leadless package (QLP or QFN) that is 7mm square. It is powered with  $\pm 3.0 \mathrm{V_{CC}}$  supply. The CC2420 has an internal 1.8V low drop out regulator for powering the internal RF and analog circuitry. It consumes 20ma during receive operation and 18ma for 0dBm transmit. The frequency generation uses an accurate 16MHz crystal with  $\pm 10 \mathrm{ppm}$  accuracy,  $\pm 10 \mathrm{ppm}$  stability and  $\pm 1 \mathrm{ppm}$  aging. The entire RF section is enclosed in an upper and lower RF shield and has modular FCC approval.

802.15.4 channel assignments are shown in the tables below.

| Channel | Center Frequency |

|---------|------------------|

| 11      | 2405MHz          |

| 12      | 2410MHz          |

| 13      | 2415MHz          |

| 14      | 2420MHz          |

| 15      | 2425MHz          |

| 16      | 2430MHz          |

| 17      | 2435MHz          |

| 18      | 2440MHz          |

| Channel | Center Frequency |

|---------|------------------|

| 19      | 2445MHz          |

| 20      | 2450MHz          |

| 21      | 2455MHz          |

| 22      | 2460MHz          |

| 23      | 2465MHz          |

| 24      | 2470MHz          |

| 25      | 2475MHz          |

| 26      | 2480MHz          |

The output power can be adjusted by the PA LEVEL register, a 6 bit field.

PA Level and output power are shown in the tables below.

| PA_LEVEL | Output Power |

|----------|--------------|

| 31       | 0dBm         |

| 27       | -1dBm        |

| 23       | -3dBm        |

| 19       | -5dBm        |

| PA_LEVEL | Output Power |

|----------|--------------|

| 15       | -7dBm        |

| 11       | -10dBm       |

| 7        | -15dBm       |

| 3        | -25dBm       |

For more information, see the CC2420 data sheet on the www.ti.com (RF/IF Components) or www.chipcon.com. The 802.15.4 standard can be retrieved from standards.ieee.org.

#### Antenna

The antenna is an inverted-F antenna printed on the top layer of the printed circuit board. It is tuned to 2450MHz and has a characteristic input impedance of  $115\Omega$  unbalanced. This is a folded monopole  $\chi$ 4 wave with reasonable omnidirectional radiation. The antenna is matched to the balanced RF output of the CC2420 using a lumped-LC network. The RF output is also biased by the TXRX\_SWITCH output of the CC2420 through a RF blocking filter.

The antenna section of the eSPOT should be kept away from all metal objects. If mounted on a motherboard, there should be no PCB traces or power planes under or around the antenna section. If possible, the eSPOT should be mounted so that the antenna is located on the edge of the board.

The FCC certification does not allow an external antenna to be connected to the eSPOT.

## eSPOT Daughterboards

The supplied eDemo board is a single example of the class of daughterboards which may be connected to the eSPOT main board. Any eSPOT daughterboard must have at least the following characteristics:

- Connect to the eSPOT main board with a Hirose DF17-30 connector

- Act as an SPI slave in communication with the eSPOT main board

- Contain SPI flash memory for storing configuration information

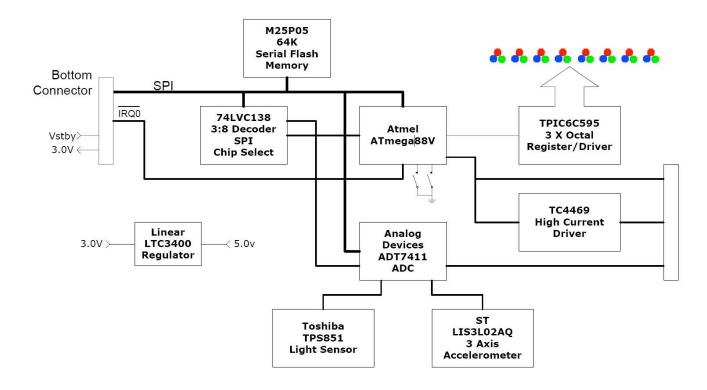

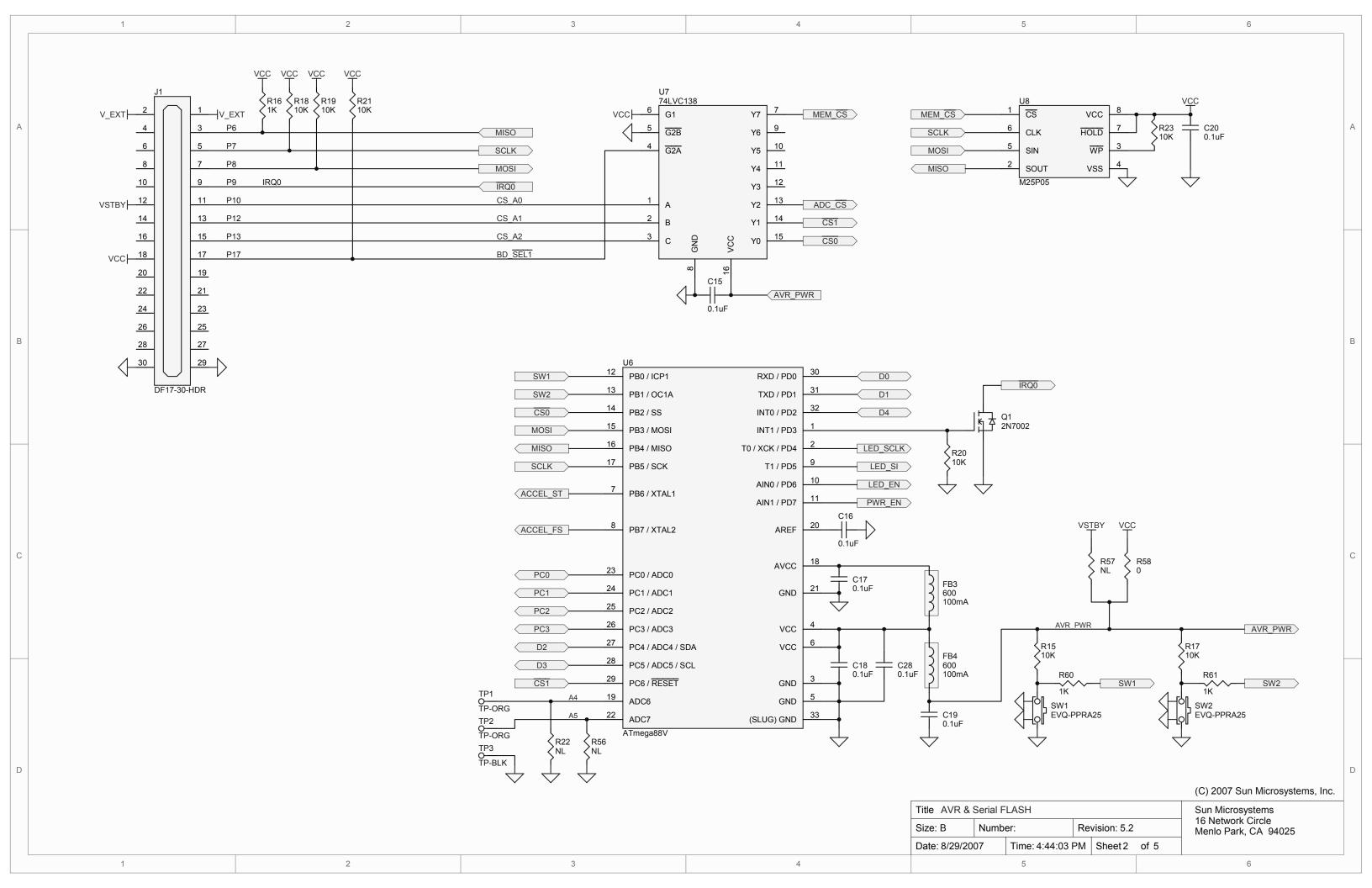

Communication from the main board to any daughterboard is done through the SPI channel. The main board select is BD\_SEL1. This is an addressable control signal which uses signals CS\_A0 - CS\_A2 as the address lines of a 3-to-8 decoder (74LVC138). The chip selects are enabled when BD\_SEL1 is asserted active low.

The three-bit chip select address allows eight devices for each board select. CS\_A2, CS\_A1, and CS\_A0 must be selected and stable prior to BD\_SELx asserted and remain stable until after BD\_SELx is deasserted. For stacking boards, BD\_SEL1 selects the board nearest the main board, and BD\_SEL2 selects the stacking board. BD\_SEL1 is used when only one application board is present.

Every application board is required to have a small SPI flash selectable when  $CS_A0 = '1'$ ,  $CS_A1 = '1'$ , and  $CS_A2 = '1'$ . This memory is for board identification and configuration information.

## eDemo Board Hardware

The supplied eDemo board is an example from the possible universe of eSPOT daughterboards. It contains an Atmega88 processor, flash memory, a light sensor, a temperature sensor, an accelerometer, eight tri-color LEDs, and two switches.

The Atmel Atmega88 microcontroller communicates with the main board ARM9 over the SPI channel as a slave device. The Atmega88 controls the LEDs, provides general multifunction input/output pins, interrupts the ARM9, controls mode bits on the accelerometer, scans analog inputs and reports digitized values. New firmware for the eDEMO board can be loaded over the SPI channel.

The chip select address truth table is shown below.

| BD_SEL1 | CS_A2 | CS_A1 | CS_A0 | Function                             |

|---------|-------|-------|-------|--------------------------------------|

| 1       | Х     | Х     | Х     | No Operation                         |

| 0       | 1     | 1     | 1     | Select configuration memory          |

| 0       | 1     | 1     | 0     | Reserved                             |

| 0       | 1     | 0     | 1     | Reserved                             |

| 0       | 1     | 0     | 0     | Reserved                             |

| 0       | 0     | 1     | 1     | Reserved                             |

| 0       | 0     | 1     | 0     | Select ATD7411 ADC (ADC_CS)          |

| 0       | 0     | 0     | 1     | Select Atmega88 RESET (Program mode) |

| 0       | 0     | 0     | 0     | Select Atmega88                      |

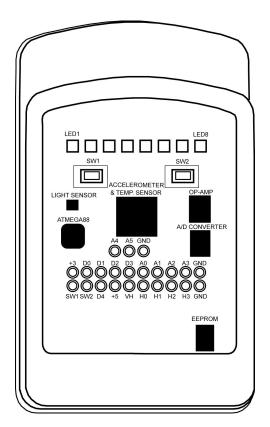

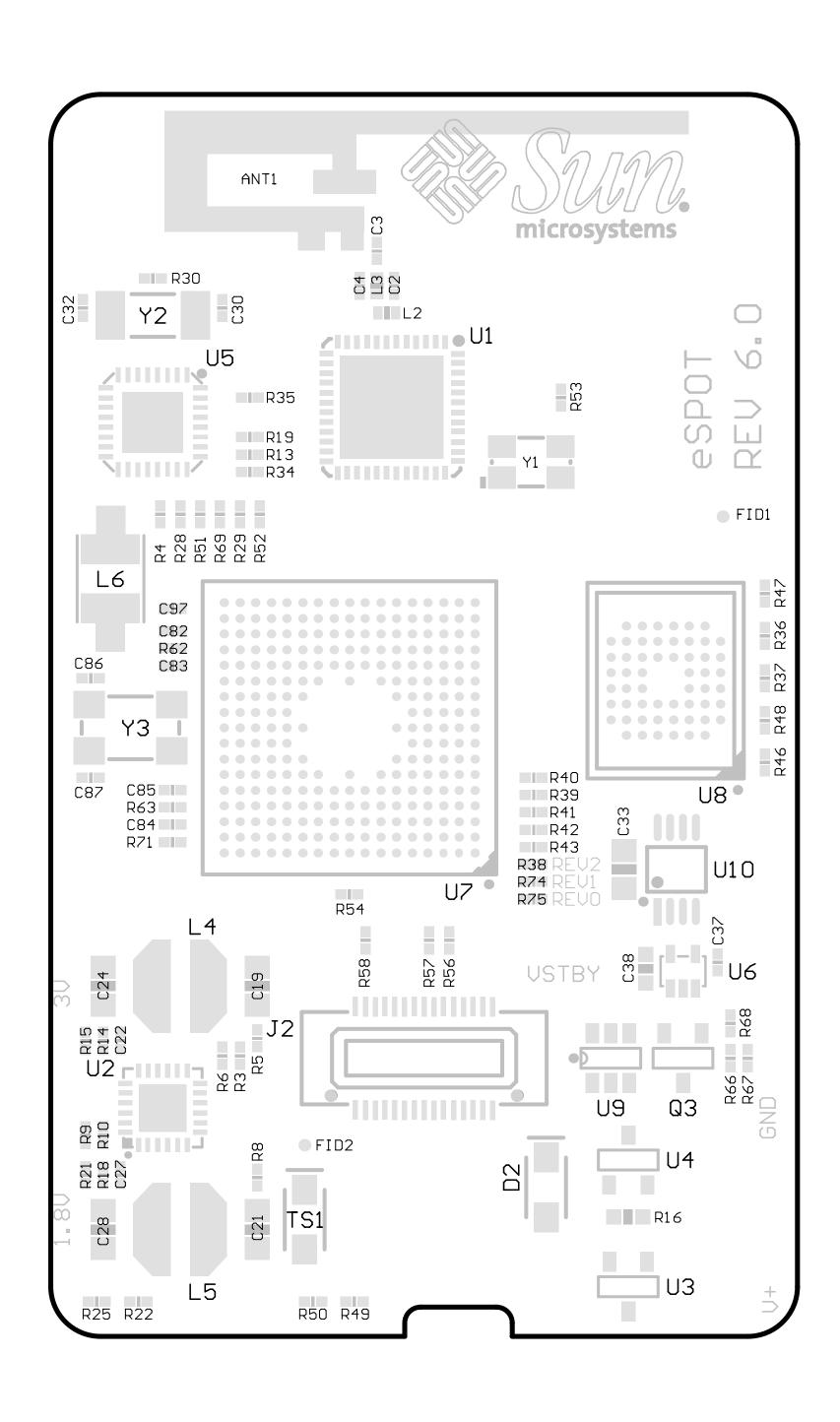

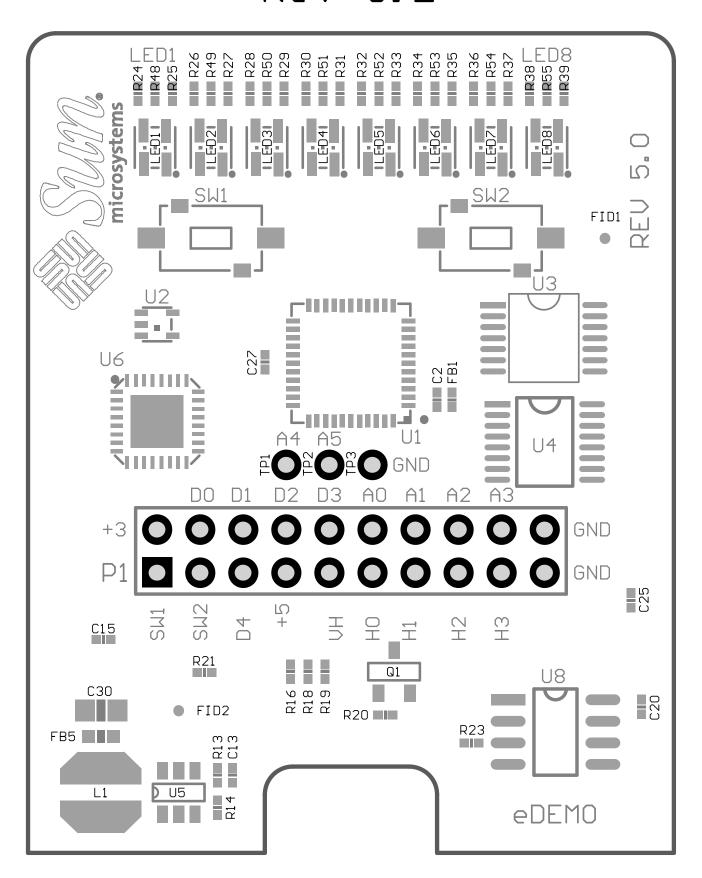

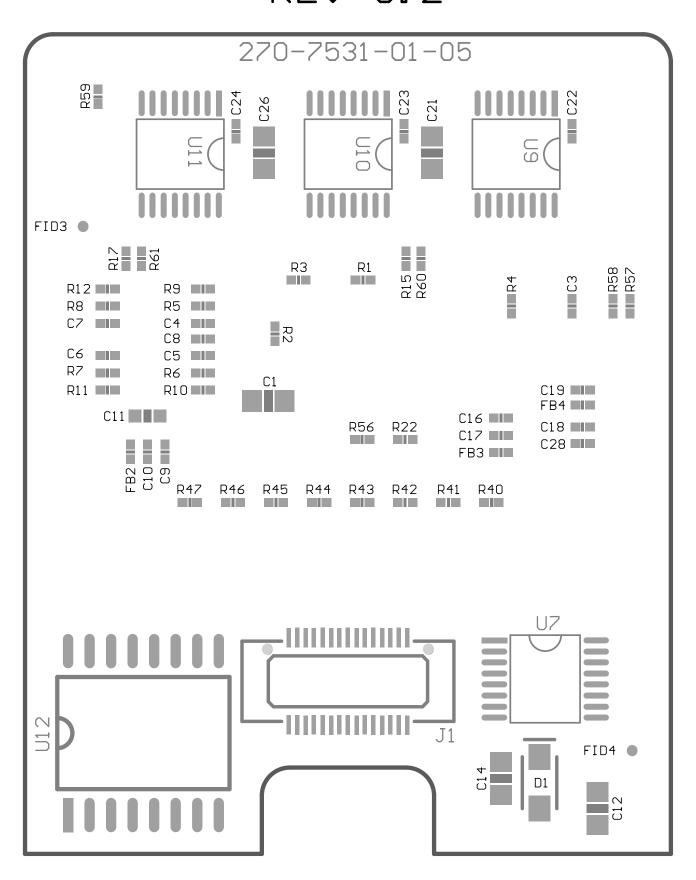

The eDemo board component locations are illustrated below.

#### **I/O Connector Pinout P1**

|                                                     |                  |       | 1               |

|-----------------------------------------------------|------------------|-------|-----------------|

| V <sub>CC</sub> +3VDC Output 100ma Maximum          | SW1              | 1 2   | V <sub>cc</sub> |

| V <sub>+5V</sub> +5VDC Output 100ma                 | SW2              | 3 4   | D0              |

| V <sub>H</sub> +4.5V to 18VDC Input                 | D4               | 5 6   | D1              |

| A0-3 Analog Input 10 bit 0V to 3.0VDC               | $V_{+5V}$        | 7 8   | D2              |

| D0-4 GPIO                                           | $\mathbf{V}_{H}$ | 9 10  | D3              |

| H0-3 High Current Output 125ma 0V to $V_{\text{H}}$ | но               | 11 12 | A0              |

|                                                     | H1               | 13 14 | A1              |

|                                                     | H2               | 15 16 | A2              |

|                                                     | НЗ               | 17 18 | А3              |

|                                                     | GND              | 19 20 | GND             |

|                                                     |                  |       |                 |

The I/O connector is designed for a 20-pin through-hole 0.1" center header.  $V_{\text{CC}}$  comes from the eSPOT. V+5 is generated on the eDEMO board.

## **Configuration Memory**

All application boards have a serial EEPROM memory for storing configuration information. On the eDEMO board this is an SPI EEPROM 64K x 8 U8 which is enabled when CS\_A2-CS\_A0 = '111'. This memory can be written to and read from.

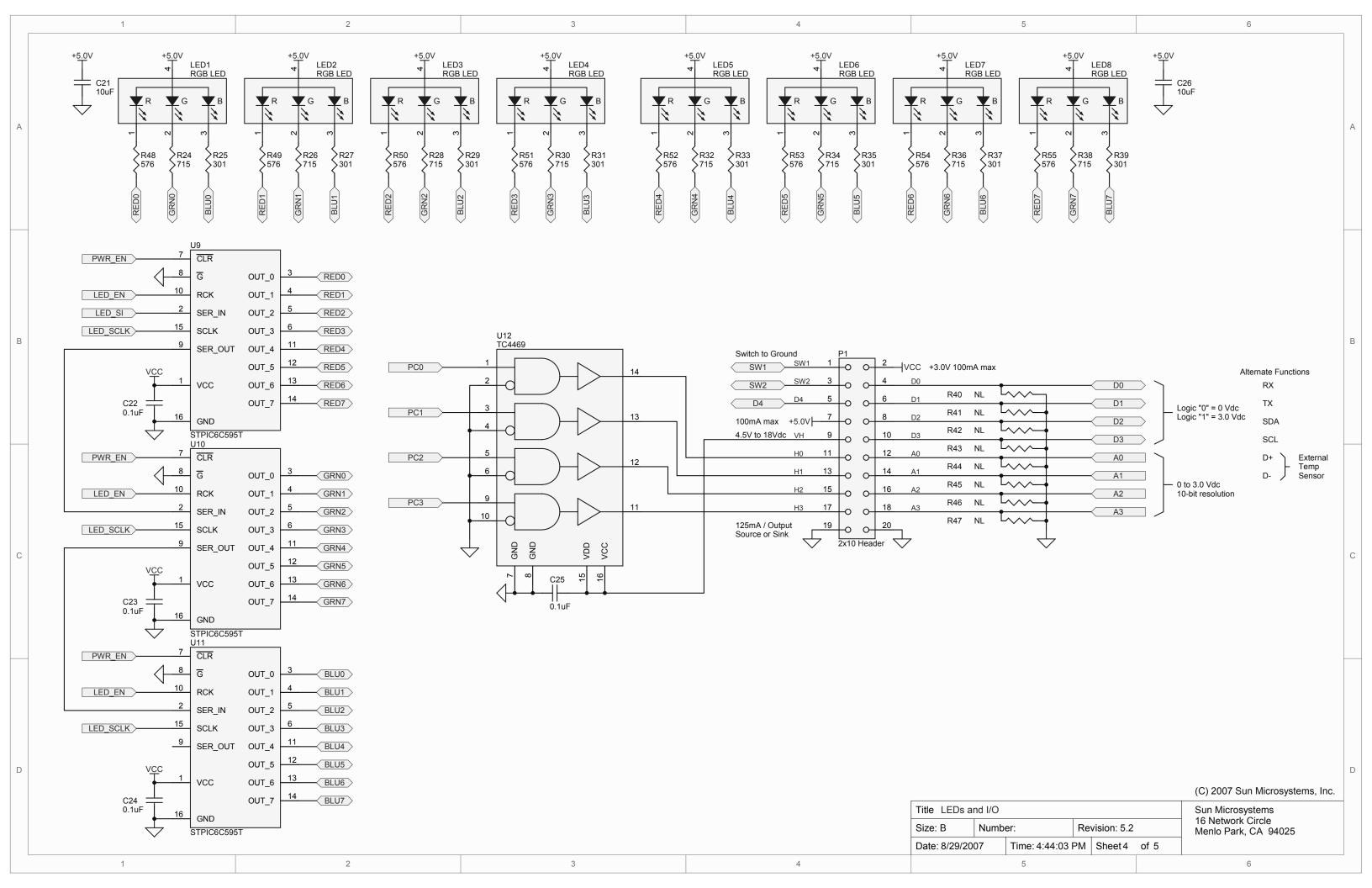

#### **LEDs**

Along the top of the eDEMO board is a row of eight tricolor (red-green-blue) LEDs LED1-LED8. These LEDs are driven by octal driver/registers STPIC6C595 U9-U11. The driver/registers are serially loaded by the on-board Atmega88. The synchronous serial stream to the LEDs is RED0-RED7, GREEN0-GREEN7 and BLUE0-BLUE7. After the 24bits are shifted in, the LED\_EN broadside loads the shifted bits to the LEDs. This register is reloaded every 255µs and the bits are pulse-width modulated in firmware to vary the individual intensity of each LED. The LED intensities are set by SPI commands from the ARM9.

#### **Push Buttons**

Below the LEDs are two tactile momentary SPST normally open push buttons, SW1 and SW2. These are scanned by the Atmega88 processor and can report the state of the push button to the ARM9 over SPI. The push buttons are pulled up to +3V, either  $V_{CC}$  or  $V_{stby}$  and are high to AVR port pins PB0 and PB1. Pushing a button pulls the signal on PB0 or PB1 to ground. The push buttons signals go to connector P1 pin 1 (SW1) and P1 pin 3 (SW2) through 1K ohm resistors. These pins can either be input to the eDEMO board and parallel the operation of the push buttons, or they can passively monitor the push buttons as outputs.

#### **GPIO**

The general purpose digital I/O lines may be configured as either inputs or outputs. D0 and D1 may also be used as UART data lines RX and TX. D2 and D3 may also be used as I2C-DATA and I2C-CLOCK, respectively.

The current limitations on the GPIO lines depend on the temperature of the Sun SPOT. At room temperature, the limits are source current, 16ma; sink current, 24ma. For other temperatures, see the Atmega88 datasheet, assuming 3.0v to the Atmega88.

## **High Current Driver**

Four signals from the Atmega88 PC0-PC3 are buffered by a high current driver, Microchip TC4469. The outputs, H0-H3, are totem-poll capable of sinking and sourcing 125ma. The high voltage output is set by  $V_H$  which is externally connected to P1 pin 9.  $V_H$  is between +4.5V to +18VDC and must be connected to a positive supply for H0-H3 to function.

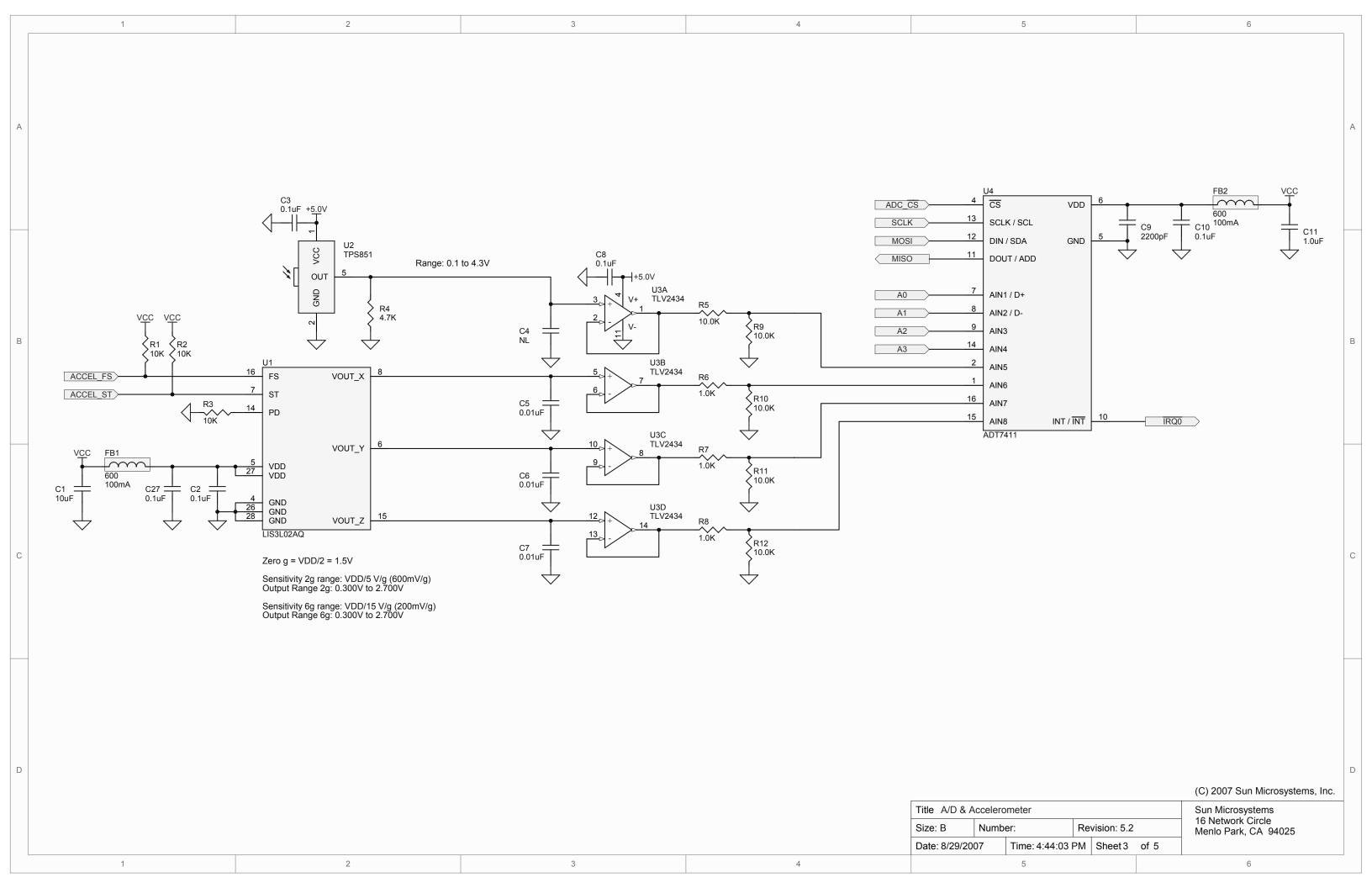

## Analog to Digital Conversion

The Analog Devices ADT7411 ADC converts analog inputs from the accelerometer, light sensor, and its own internal temperature sensor to digital values that can be read by SPOT applications. The ADC is also available to encode analog inputs from pins A0, A1, A2, and A3.

The analog inputs are designed to accept a 0 - 3Vdc analog voltage.

The resolution is

$$ADC = \frac{V_{in} \cdot 1024}{V_{ref}} 1.024 \text{mV/count.}$$

V<sub>ref</sub> is 3.0V.

## Temperature Sensor

The ADT7411 ADC contains an internal temperature sensor that is capable of measuring temperatures in the range –40 to +125 degrees Celsius with an accuracy of 0.25 degrees Celsius. To convert the raw temperature reading to degrees Celsius:

Positive Temperature = ADC / 4 (when ADC < 512)

Negative Temperature = (ADC - 1024)/4 (when ADC >= 512)

Because the temperature sensor is part of the ADT7411 chip, it actually measures the temperature on the chip, which is generally slightly different than the surrounding environment, especially during USB charging. The sensor gives the most accurate temperature readings immediately after the Sun SPOT wakes up from deep sleep, when not connected to USB.

In revision 6.0 SPOTs, a more accurate temperature sensor was added on the main board, and is read from the power controller. Run ant info to check revision.

## Accelerometer

The eDEMO board contains the ST Microsystems 3-Axis 2g/6g Inertial Sensor LIS3L02AQ. The Z axis is perpendicular to the boards surface, the Y axis is parallel with the boards surface perpendicular with the row of LEDs, and the X axis is parallel with the row of LEDs. The orientation of X, Y, and Z accelerometer axes is illustrated below.

The accelerometer has three voltage outputs  $V_{out\_x}$ ,  $V_{out\_y}$ , and  $V_{out\_z}$  representing acceleration in 3-axis. The force accelerating the SPOT in any dimension, measured in g-force units, is:

$$g = \frac{ADC - 465.5}{186.2}$$

These are filtered by a single pole filter  $(0.01\mu \text{ F capacitor})$  and buffered by non-inverting op amp U3. The output of the op-amp is voltage divided by a 10/11 ratio with a 1.0K and 10.0K 1% resistors and is the input to channels 6(x), 7(y), and 8(z) of the ADC U4 (ADT7411). Taking the ratio into account,

$$ADC = \frac{V_{in} \cdot (10/11) \cdot 1024}{V_{ref}} = \frac{V_{in} \cdot 931}{V_{ref}}$$

The accelerometer output reference is  $0g = V_{dd}/2 = 1.5V$  with 2g sensitivity of (VDD/5)V/g or  $600mV/g \pm 10\%$ , 6g sensitivity of  $(V_{DD}/15)V/g$  or 200mV/g and a range of 0.3 to 2.7V. At the ADC the range is 272mV to 2.455V and 0g at 1.364V. Sensitivity is 545mV/g at the ADC for 2g and 182mV/g for 6g. Nominal 0g read from the ADC is 466.

$$V_{acc} = (600mV \cdot g) + 1500mV$$

$$ADC = \frac{\left((600mV \cdot g) + 1500mV\right) \cdot \left(\frac{10}{11}\right) \cdot 1024\right)}{V_{ref}}$$

$$ADC = 186.2g + 465.5 \qquad for \qquad V_{ref} = 3.0V$$

$$g = \frac{(ADC - 465.5)}{186.2}$$

For each axis, the maximum sample rate is 160Hz. The capacitors C5-C7 provide a single pole low pass filter to bandlimit the accelerometer. The frequency of this limit is

$$F_t = \frac{1}{2\pi \cdot R_{out} \cdot Cf(x, y, z)}$$

C5-C7 are  $0.01\mu$  F capacitors and  $R_{out}$  is 100K internal resistance of the accelerometer. Therefore the cutoff frequency  $F_t$  is 160Hz.

## Accelerometer Self Test

The accelerometer has a self test mode which physically biases the internal "slug" with electrostatic energy. Self test is the measured difference between normal mode and self-test mode. Self-Test mode is entered when the self-test pin is set to a '1'. During these test, the accelerometer must be stationary. Two

readings are taken of all three axis. The first reading is in normal mode, the second is in "self-test" mode. The difference between normal and self-test mode for each axis must fall within a specified range (see the table below). This test is performed in both 2g and 6g settings.

| Mode | Axis   | Voltage Range  | Reading   |

|------|--------|----------------|-----------|

| 2g   | X_axis | -20mV to -40mV | -6 to -13 |

| 6g   | X_axis | -6mV to -14mV  | -1 to -5  |

| 2g   | Y_axis | 20mV to 40mV   | 6 to 13   |

| 6g   | Y_axis | 6mV to 14mV    | 1 to 5    |

| 2g   | Z_axis | 20mV to 50mV   | 6 to 16   |

| 6g   | Z_axis | 6mV to 17mV    | 1 to 6    |

## Light Sensor

Mounted on top of the eDemo board is a Toshiba TPS851 light to voltage sensor. Output of the sensor is 0.1V to 4.3V, dark to light, using a emitter resistor of 4.7K (R4). This voltage is buffered by op-amp U3 (TI TLV2434) and divided by 2 by resistor divider R5 and R9. Output of the resistor divider is input to channel 5 of ADC U4 (ADT7411) with an effective range of 0.05V to 2.15V. Peak sensitivity of the light sensor is 600nm. >3dB sensitive is  $\pm 45^{\circ}$  and switching time is  $\sim 30\mu$ sec. The specified typical values for light in luminance (lx) versus voltage are shown in the table below.

| Luminance | Light Sensor Voltage | ADC Voltage | Raw ADC |

|-----------|----------------------|-------------|---------|

| 1000 lx   | 2.914V               | 1.457V      | 497     |

| 100 lx    | 0.291V               | 0.146V      | 50      |

| 10 lx     | 0.029V               | 0.014V      | 5       |

$Lux \approx 2 \cdot ADC$

## **Electrical Characteristics**

## Absolute Maximum Ratings

| Feature                                          | Absolute Maximum Ratings |

|--------------------------------------------------|--------------------------|

| Operating Temperature (with battery charging)    | 0 to 45°C                |

| Operating Temperature (with battery discharging) | -20 to 60°C              |

| Operating Temperature (without battery)          | -20°C to +75°C           |

| Storage Temperature (with battery)               | -20°C to +35°C           |

| Storage Temperature (without battery)            | -40°C to +85°C           |

| Voltage on any input pin                         | -0.1V to 3.5V            |

| eDEMO DC Current per I/O pin                     | 40.0ma                   |

| eSPOT DC Current per I/O pin                     | 8.0ma                    |

| Maximum External/USB voltage                     | 6.0V                     |

## DC Characteristics - eSPOT J2 Connector

| Symbol            | Description                         | Condition                                                                   | Min            | Тур            | Max             | Units          |

|-------------------|-------------------------------------|-----------------------------------------------------------------------------|----------------|----------------|-----------------|----------------|

| V <sub>ext</sub>  | External Voltage                    |                                                                             | 4.2            | 5.0            | 5.5             | V              |

| V <sub>batt</sub> | Battery Voltage                     |                                                                             | 3.1            | 3.7            | 4.2             | V              |

| V <sub>usb</sub>  | USB Voltage                         |                                                                             | 4.2            | 5.0            | 5.5             | V              |

| l <sub>usb</sub>  | USB Current Limit                   | V <sub>usb</sub> = 5.0V, USBHP = '1'<br>V <sub>usb</sub> = 5.0V, USBHP = '0 | 440<br>60      | 475<br>80      | 500<br>100      | ma<br>ma       |

| I <sub>ext</sub>  | External Current                    | V <sub>ext</sub> = 5.0V, no eDemo<br>V <sub>ext</sub> = 5.0V, with eDemo    |                | 300<br>500     |                 | ma<br>ma       |

| I <sub>batt</sub> | Battery Current - no attached board | Deep Sleep<br>Idle<br>Normal                                                | 18<br>21<br>40 | 21<br>23<br>87 | 28<br>25<br>144 | µa<br>ma<br>ma |

| Symbol                | Description                          | Condition                                                                                               | Min  | Тур              | Max              | Units          |

|-----------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|------|------------------|------------------|----------------|

| I <sub>charge</sub>   | Charge Current                       | V <sub>usb</sub> = 5.0V, USBHP = '1'<br>V <sub>usb</sub> = 5.0V, USBHP = '0'<br>V <sub>ext</sub> = 5.0V | 425  | 400<br>50<br>500 | 470<br>90<br>575 | ma<br>ma<br>ma |

| V <sub>low_batt</sub> | Low battery indication               |                                                                                                         |      | 3.25             | V                |                |

| I <sub>stby_max</sub> | Externally available standby current | J2-11 V <sub>stby</sub> = 3.0V                                                                          |      |                  | 5                | ma             |

| I <sub>cc</sub>       | Attached board current               | V <sub>CC</sub> = 3.0V                                                                                  |      |                  |                  | ma             |

| V <sub>OL</sub>       | Output low level voltage             | I <sub>OL</sub> = 0 to 8ma                                                                              | 0.2  | 0.3              | 0.4              | V              |

| V <sub>OH</sub>       | Output high level voltage            | I <sub>OH</sub> = 0 to 8ma                                                                              | 2.6  | 2.7              | 2.8              | V              |

| V <sub>IL</sub>       | Input low level voltage              |                                                                                                         | -0.3 |                  | 0.8              | V              |

| V <sub>IH</sub>       | Input high level voltage             |                                                                                                         | 2.0  |                  | 2.7              | V              |

## DC Characteristics - eDEMO I/O Connector P1

| Symbol           | Description                                  | Condition                    | Min                   | Тур | Max        | Units    |

|------------------|----------------------------------------------|------------------------------|-----------------------|-----|------------|----------|

| V <sub>ext</sub> | External Voltage                             |                              | 4.2                   | 5.0 | 5.5        | V        |

| l <sub>ext</sub> | External Current                             | V <sub>ext</sub> = 5.0V      |                       |     |            | ma       |

| I <sub>cc</sub>  | eDEMO current from main board.               | V <sub>cc</sub> = 3.0V       |                       |     | 250        | ma       |

| V <sub>+5V</sub> | 5V output from eDEMO at P1-7                 | V <sub>+5V</sub> = +5.0V     |                       |     | 100        | ma       |

| V <sub>H</sub>   | H0-H3 high level voltage                     |                              | 4.5                   |     | 18         | V        |

| V <sub>OL</sub>  | Output low level voltage (except for H0-H3)  | I <sub>OL</sub> = 6ma        | -                     | _   | 0.5        | V        |

| V <sub>OH</sub>  | Output high level voltage (except for H0-H3) | I <sub>OH</sub> = 10ma       | 2.3                   | _   | _          | V        |

| V <sub>OL</sub>  | Output low level voltage for H0-H3           | I <sub>OL</sub> = 0 to 8ma   | -                     | _   | 0.15       | V        |

| V <sub>OH</sub>  | Output high level voltage for H0-H3          | I <sub>OH</sub> = 0 to 8ma   | V <sub>H</sub> -0.025 | _   | _          | V        |

| I <sub>H</sub>   | H0-H3 output current sink/source             | Single output<br>All outputs |                       |     | 300<br>500 | ma<br>ma |

| V <sub>IL</sub>  | Input low level voltage                      | All inputs                   | -0.5                  | _   | 0.9        | V        |

| V <sub>IH</sub>  | Input high level voltage                     |                              | 1.8                   | _   | 2.5        | V        |

| V <sub>ANA</sub> | Input voltage range                          |                              | 0.0                   |     | 3.0        | V        |

## eDemo Software

The eDemo board contains an Atmega88 micro-controller. This section describes the functions implemented in the Atmega88 firmware.

## **Overall Operation**

The Atmega88 operates the eight tricolor LEDs, the accelerometer configuration, and the following pins on the I/O header:

```

D0, D1, D2, D3, D4,

H0, H1, H2, H3, SW1, SW2,

ADC4, ADC5, GND.

```

The Atmega88 communicates with the main board using an SPI interface. The Atmega88 also controls an interrupt line to the power controller on the main board.

The Atmega88 operates with an 8MHz instruction clock. Every 256ms, the controller runs its process loop to execute the tasks currently enabled. When all the tasks are completed, the processor goes to sleep until the next process interrupt.

## **Functions**

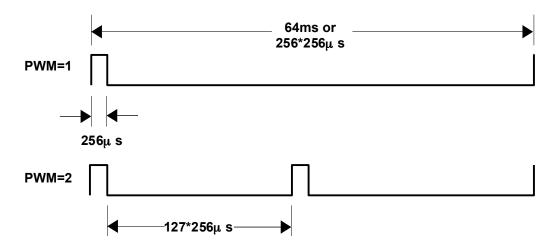

#### Pulse Width Modulation

This function supports pulse width modulation (PWM) on up to eight I/O pins simultaneously. For any particular pin, PWM value may be set to any integer between 1 and 255. The output state is high for that number of evenly spaced periods of 256ms out of a 64ms cycle.

If the value is one, the output is high for 256ms and low for (255\*256)ms. When the value is two, the output is high for 256ms, low for (127\*256)ms, high for 256ms, and low for (127\*256)ms. When the value is 128, the output is toggled between 1 and 0 every 256ms.

#### LEDs

Each of the eight tri-color LEDs can be pulse width modulated using the PWM mechanism described above. Each of the red, green, and blue LEDs is separately controllable. The minimum value is limited to 3 to mitigate visible flicker.

If the Atmega88 processor is unable to complete all the tasks enabled in its process loop, it suspends PWM of the LEDs temporarily.

#### Pulse Width Generation

A one-shot pulse can be generated on any output pin, with a pulse width ranging from  $1\mu$ s to  $65536\mu$ s. The pulse may be either positive (0 > 1 > 0) or negative (1 > 0 > 1). Only one pulse may be active at a time.

#### Pulse Width Detection

The duration of a pulse may be measured on any input pin, with the pulse width range from  $1\mu$ s to 65536ms. Pulses longer than 65536 $\mu$ s are recorded as 65536ms. As with pulse width generation above, the pulse may be either positive or negative. Only one pulse measurement may be active at one time.

#### Tone Generation

A square wave may be generated on any output pin. The frequency of the square wave is determined by the equation:

$$freq = \frac{500000}{N}$$

where N is the number input to the tone generator.

The period of the square wave is from 1 to 65536 units, where 1 unit is  $2\mu s$ . To minimize the CPU load on the micro-controller, the current implementation has a minimum period of 129 units. Only one tone generator may be active at one time.

#### Servo Controller

Eight output pins may be configured to drive standard servos. For each servo configured output pin, a pulse is generated every  $32\mu s$ . The pulse width generator (described above) is used to generate the pulses, and is not available separately when the servo controller is active. The pulse width is specified in  $\mu s$  and a typical value is between  $1000\mu s$  and  $2000\mu s$ .

Servo would ordinarily be connected to a Sun SPOT by

- Connecting the ground wire from the servo connector to the ground pin on the IO header

- Connecting the data wire to one of the data input/output pins (D0 to D3) or the high output pins (H0 to H3)

• Connecting the servo to a external power source

The following code fragment illustrates the steps to initiate a servo attached to pin D1 and set a pulse width for that servo.

```

import com.sun.spot.sensorboard.EDemoBoard;

import com.sun.spot.sensorboard.capabilities.IServoController;

import com.sun.spot.sensorboard.io.IOutputPin;

import com.sun.spot.sensorboard.peripheral.IServo;

// Get the demo board itself

EDemoBoard ourDemoBoard = EDemoBoard.getInstance();

// Create an object to hold the particular pin of interest

// on the demo board

IOutputPin servoOutPin = ourDemoBoard.bindOutputPin(

ourDemoBoard.getInstance.().D1);

// Bind a servo to that output pin

IServo ourServo = ourDemoBoard.bindServo(servoOutPin);

// Set the output pulse length to use for that servo

ourServo.setValue(1300);

// Also declare a relative position for that output pulse length

ourServo.setPosition(0.5);

// Now we can manipulate the servo by setting the pulse width or by setting the

position as a floating point number between 0 and 1.

```

## Analog/Digital Conversion

The pins A0 to A3 are connected to the A/D converter (ADC) on the eDemo board. These can be read in software. If ADC is the digital output value of the A/D converter (ADC),  $V_{in}$  is the input voltage read by the ADC, and  $V_{ref}$  is the reference voltage for the ADC, then the relationship of the input voltage to output word is:

$$ADC = \frac{V_{in} \cdot 1024}{V_{ref}}$$

$V_{ref}$  is currently the external 3.0V  $V_{CC}$ .

## Interrupt Detection

The Atmega88 can be configured to assert (hold low) the IRQ0 pin which is attached to the main board, when the logic level changes on any (or all) of the input pins. Each input pin may be configured separately to generate the interrupt from a low > hi transition, a hi > low transition, or both. The pin (or pins) that generated the interrupt may be queried via the SPI bus from the main board.

#### EEPROM Access

Any byte in the lower 256 bytes of EEPROM may be read or written, one byte at a time.

## I/O Pin Manipulation

I/O pins D0 through D3 can be set as either an output or input. The high current driver pins, H0 to H3, can only be used as an output. If configured as an output, the pin may be set hi, low, or toggled to its opposite state.

#### Register Control

All the Atmega88 special function registers (SFRs) can be manipulated directly. When writing, the written value may used to set the register value, or it may be used as a mask. As a mask, it may be used to set or clear the bits of the SFR.

#### Memory

Any flash location may be read.

#### Miscellaneous Functions

There are several miscellaneous functions that are used for administration and testing. They include fetching a version number, setting the standalone ADC scale and test modes, and returning some aspects of the internal state of the firmware.

The A4 and A5 pins are not on the I/O header but may be used for A/D conversion. The voltage reference, input scale, and pin number may be selected. Each reading is a one-shot; continuous readings are not supported.

## Federal Communications Commission Compliance

**NOTE:** This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try and correct the interference by one or more of the following measures: Reorient or locate the receiving antenna. Increase the separation between the equipment and receiver. Connect the equipment into an outlet on a circuit different from that to which the receiver is connected. Consult the dealer or an experienced radio/TV technician for help.

The Sun SPOTs are supplied with a shielded USB cable. Operation with a non-shielded cable could cause the Sun SPOTs to not be in compliance with the FCC approval for this equipment. The antenna used with this transmitter must not be co-located or operated in conjunction with any other antenna or transmitter; to do so could cause the Sun SPOTs to not be in compliance with the FCC approval for this equipment. Any modifications to the Sun SPOTs themselves, unless expressly approved, could void your authority to operate this equipment.

#### FCC Declaration of Compliance:

Responsible Party:

Sun Microsystems, Inc.

4150 Network Circle

Santa Clara, CA 95054

Phone: US 1-800-555-9786; International 1-650-960-1300

Products:

SLS-E5-XXXX

where "X" is any alphanumeric character or a blank.

This device complies with Part 15 of the FCC Rules. Operation is subject to the following conditions: this device may not cause harmful interference and this device must accept any interference received, including interference that may cause undesired operation.

This device can be used as is (stand-alone) or as a module (part of a final host product). If the device will be used as a module these rules must be followed:

#### 1. Integrator must place a label outside their product similar to the example shown:

OEM manufacturer name

Contains transmitter module FCC ID: UDM3011 UPN: 1894B-3011 Model: 3011

#### 2. Caution: Exposure to Radio Frequency Radiation

To comply with FCC RF exposure compliance requirements, a separation distance of at least 20 cm must be maintained between the antenna of this device and all persons. This device must not be colocated or operating in conjunction with any other antenna or transmitter.

Module 3011 and antenna tested with must be integrated in the end product in such a way that the end user cannot access the either the module, cables, or antennas.

The installer of this radio equipment must ensure that the antenna is located or pointed such that it does not emit RF field in excess of Health Canada limits for the general population; consult Safety Code 6, obtainable from Health Canada's website <a href="https://www.hc-sc.gc.ca/rpb">www.hc-sc.gc.ca/rpb</a>.

## eSPOT & eDemo Board Schematics and Assembly

## eSPOT ASSEMBLY TOP REV 6.0

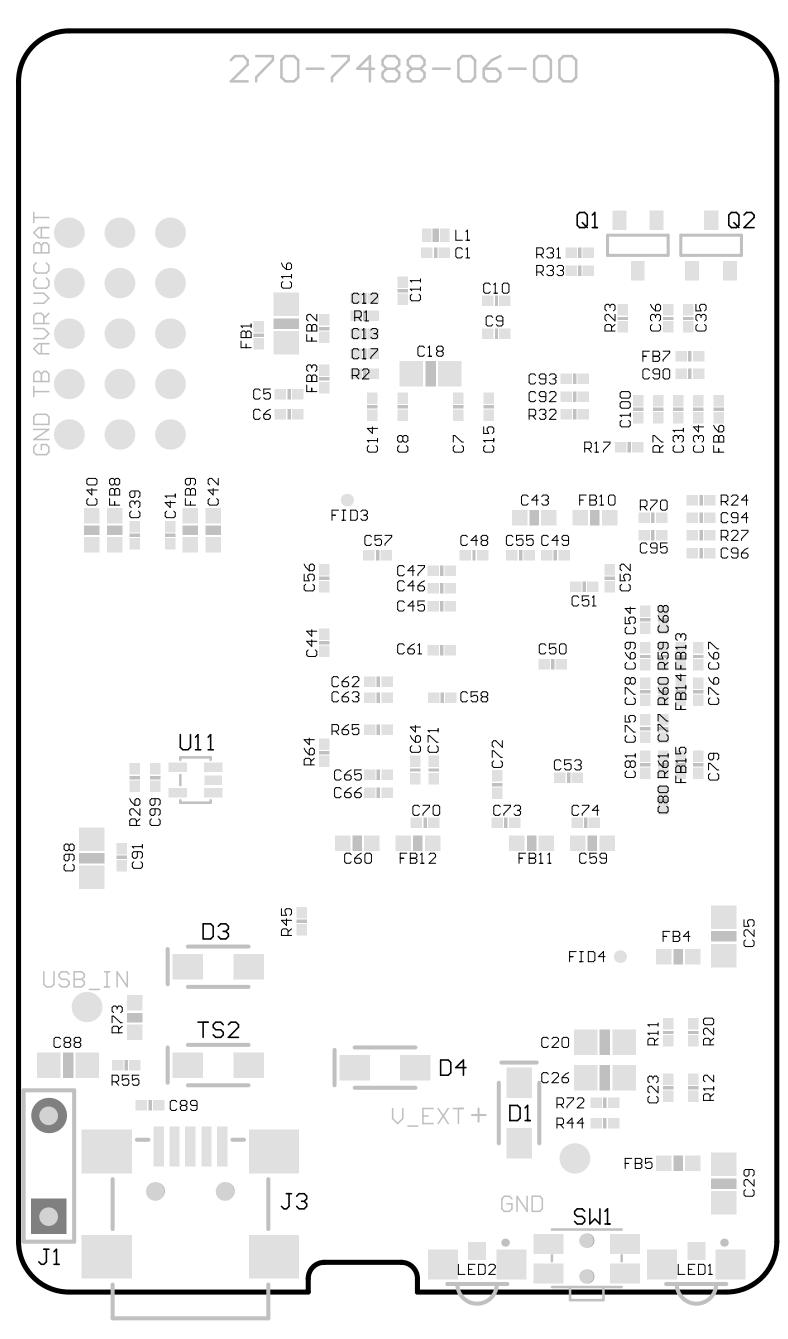

## eSPOT ASSEMBLY BOTTOM REV 6.0

(C) 2007 Sun Microsystems, Inc.

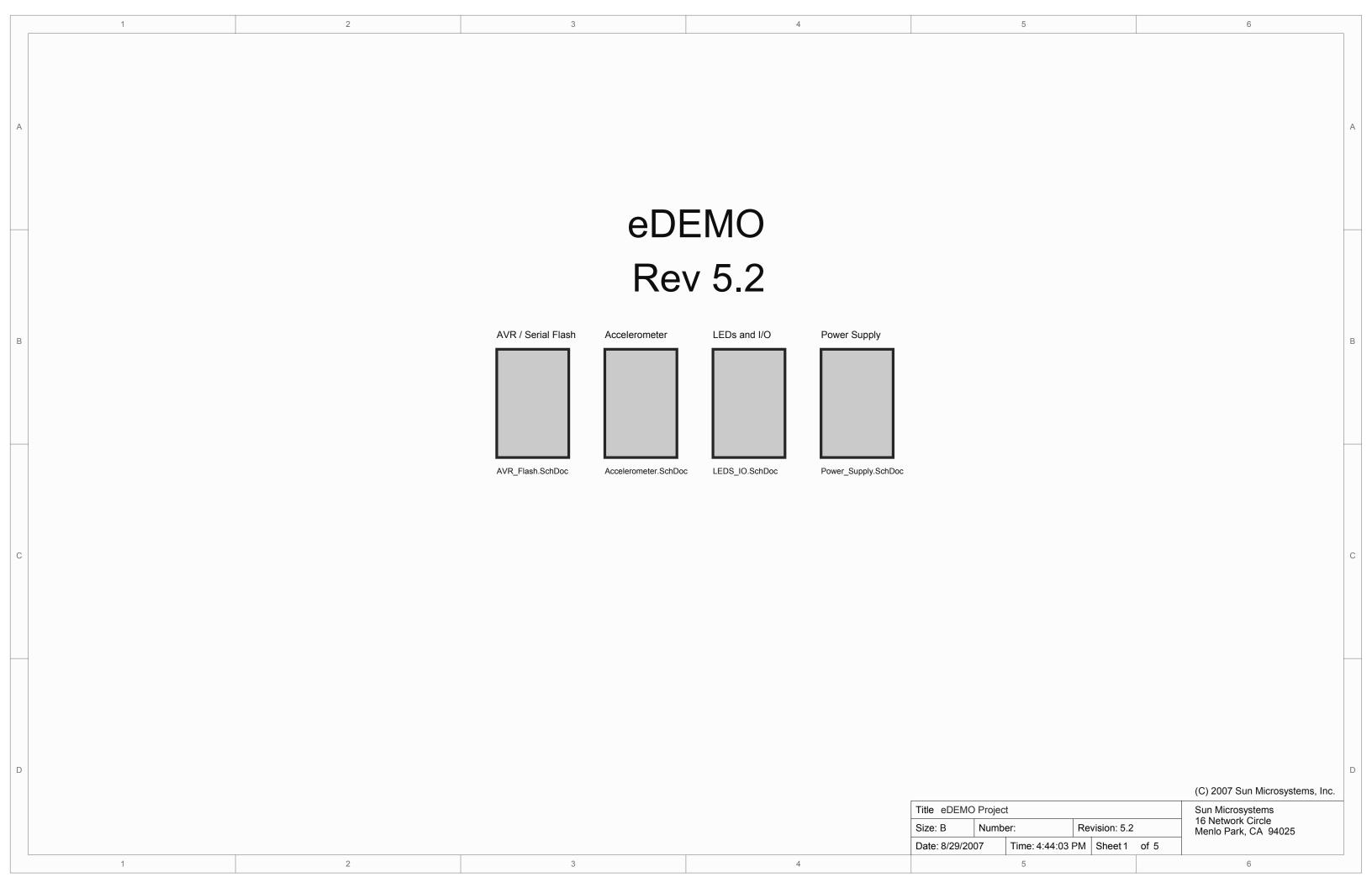

## eDEMO ASSEMBLY TOP Rev 5.2

(C) 2006 Sun Microsystems, Inc.

## eDEMO ASSEMBLY BOTTOM REV 5.2

(C) 2006 Sun Microsystems, Inc.